今回のスーパーコンピューターの系譜は、BlueGen/Pの後継であり、現在も広く使われているBlue Gene/Qを解説しよう。

このBlue Gene/QをベースとしたSequoia(セコイア)は、ASCのシステムとしてローレンス・リバモア国立研究所に導入され、2012年6月のTOP500では京コンピューターを退けて世界最速の座に着いたマシンである。

現時点での最新のリスト(2014年6月)でもまだ3位に位置しているあたり、まさに現役のアーキテクチャーである。

同時4スレッド実行可能なプロセッサーを採用した

BlueGene/Q

さて、前回の最後でも述べたが、Blue Gene/PのアーキテクチャーはBlue Gene/Lと比べてずば抜けて優れていたわけではない。

もちろんプロセスの微細化やI/Fの高速化などで性能と消費電力の両面で改善はあったものの、それは数%~数十%で、積み重ねても数倍という域には達していない。これもあって、Blue Gene/Qでは、基本的なアーキテクチャーそのものは同じながら、実装はずいぶん変化した。

基本的なアーキテクチャーとは「PowerPCベースの超並列」で、これに変化はない。使われるコアはPowerA2になった。IBMは2000年のISSCCで、ネットワークプロセッサーとしてPowerEN(Power Edge of Network)という製品を発表したが、このPowerENに使われてたのがPowerA2である。

Blue Gene/Qでは、このPowerA2コア、というよりPowerENのプロセッサー周辺部をまるごと流用したことになる。そのPowerA2コアの構造は下の画像のとおり。

In-Orderのパイプライン構成で、実行ユニットは2命令同時実行という慎ましやかなものだが、SMT(Simultaneous Multithreading:同時マルチスレッディング)で同時4スレッド実行可能というあたりがあまり一般的ではない。

もっとも当初のネットワークプロセッサーの場合、処理の大半はデータをメモリー経由で読んで、少し手を加えて送り出すという過程になるため、性能はもっぱらメモリーアクセス性能で決まる。

つまりCPUコアの大半はメモリーアクセス待ちに陥るわけで、SMTを使ってメモリーアクセス要求を効率的に出し続けることで実効性能を引き上げようという発想そのものは正しい。

実はこの考え方はHPCにもそのまま当てはまる。要するにメモリーアクセスが最終的にはボトルネックになるので、なるべくメモリーアクセスを効率よく行なわせる必要があり、このためには複数スレッドを同時に走らせることは確かに効果的である。

ただし、PowerA2そのものは浮動小数点演算をサポートしていない。そこで、これもBlue Gene/LやBlue Gene/Pと同じく外付けで「QXP」という名称のFPUを追加したのだが、この際に規模を倍増している。

これにより1サイクルあたり倍精度浮動小数点演算を8つ(MAC演算が可能なので、FPU1個あたり2演算相当)実行できるという、強烈な構成である。

これを集積したBlue Gene/Qチップの全体が下の画像だ。360mm2のダイに、合計18ものプロセシングユニット(A2+QXP)を集約しており、このうち16個が計算、1個が通信管理などOSの作業に割り当てられている。

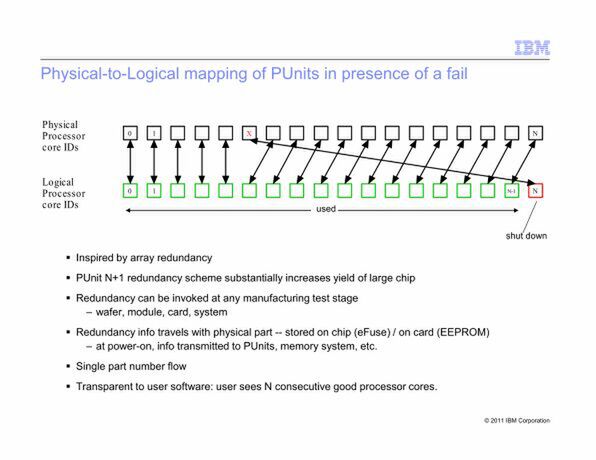

これでは合計17個になって数が合わないと思われるかもしれないが、1個は冗長コアとしてリザーブ扱いにされている。この冗長メカニズムを示したのが下の画像である。

ソフトウェアから見ると、Blue Gene/Qは17コアのプロセッサーとして見えており、不良のコアがあることは見えない。実際にはある特定のコアに問題がある場合、そのコアは無効化されるようになっているわけだ。

このあたりは、PlayStation 3で利用されていたCellプロセッサーが、実際にはSPE(Synergistic Processor Element)が8つあるにも関わらず7つのみ有効にしていたのと同じ考え方である。

(→次ページヘ続く 「チップの性能はBlue Gene/Pの15倍」)

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 - この連載の一覧へ