パイプラインはわずか6段!?

シンプルなCrusoeの構造

Crusoeは命令単位ではなく、複数命令にまたがって処理の意味を解釈するため、トランスメタの方式はインタプリタであると理解されている。CPUコア以外で近いものとしては、Javaの仮想マシンやMac OS Xに搭載されていた「Rosetta」※1、あるいはRosettaの元になったと言われている、Transitive Technologies社の「Dynamite」などが挙げられよう。もっとも、Dynamiteは「Software version of Transmeta's Code Morphing」(トランスメタのCode Morphingをソフトウェアで実現したもの)なんて言われたように、Code Morphingの方が先に登場している。

※1 インテルCPU搭載MacでPowerPC用プログラムを動かす変換処理技術。

当然ながらこうしたインタプリタを使う場合、処理のオーバーヘッドは避けられない。それは単に処理性能を落とすだけでなく、インタプリタを動かす分だけ消費電力も増加することになる。それにも関わらずCrusoeがこれを搭載したのは、「Code Morphingで最適化したら、あとは圧倒的に低い消費電力で処理を実現できる」という目算があったためだ。ではそれはいかなるものか。

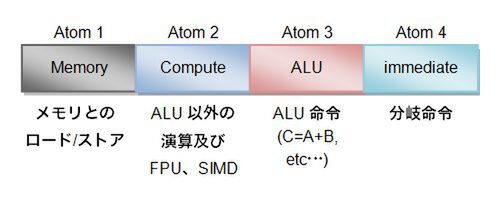

図1 Crusoeの命令フォーマット

図1はCrusoeの命令フォーマットである。Crusoeは128bitの命令幅で、32bit命令を同時に4つ処理可能となっている。ただし、この4つの命令がどういう組み合わせになるかは、厳密に決まっている。例えば「Atom 1」に入るのはMemory命令だけで、ここにALU命令を入れることはできない。その意味では、4命令同時発行といいつつも、この4つのAtomを同時に処理するというケースは非常にまれである。平均では1.x~2.x Atom/サイクルというのが、当時のトランスメタの発表であった(アプリケーションによって変わる)。

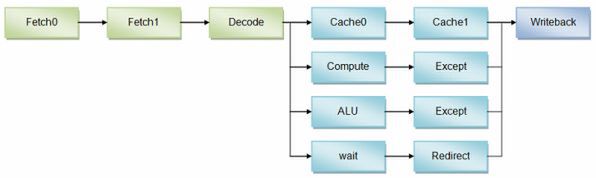

命令を処理するパイプラインは、図2のようにわずか6段しかない。文献によっては、「Writeback」の後に「Commit」というフェーズを入れて7段としていることもあるが、処理にはあまり関係ないので、ここでは割愛する。

パイプラインの最初にFetchが2つ入るが、これは128bit長の命令を、64bitずつ2回に分けて取り込むためだ。次のDecodeは命令の解釈である。といっても、CrusoeはVLIW方式で、しかもAtomごとに処理が限られているので、複雑な命令がまとめられている「Compute」に当たる「Atom 2」以外は、比較的簡単である。また、同時にレジスタからの読み込みを行なう。

次に、Atomごとに2サイクルずつを使って、それぞれを処理する。ちなみにAtom 2に関しては、整数演算に関しては1サイクルで実行できるが、浮動小数点演算だと5サイクルを要する。逆に、Atom 4の分岐は1サイクルで実行できるので、1サイクル分のウェイトを入れて帳尻を合わせている。

これらが終ったら、最後にWritebackで結果をレジスタに書き戻して終了である。x86プロセッサーのパイプラインを見慣れた人にはあっさりしているというか、こんなにシンプルでいいのかと思えるほど、簡単な構造である。x86が面倒なのは、デコード後にスケジューラーが入って命令実行順の並び替えをしたり、「ROB」(Re-Order Buffer)を使って完了した命令を管理したりといった処理を動的に行なう必要があるからだ。VLIWの場合、そうした処理をあらかじめプログラムを記述する段階で済ませるのが前提だから、ハードウェアそのものは非常にシンプルですむ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ