TLBはページテーブルエントリのキャッシュ

キャッシュ同様に階層化も進む

だが、メモリーにページテーブルを置くとなると、今度は「煩雑にアクセスが発生した場合のレイテンシーの大きさ」が問題になる。「メモリーアクセスをするためのAddress Translationに先立って、まず変換テーブルをメモリーから読み込む」というのは、実質メモリーアクセスの速度が半分に落ちるに等しい。特にCPUの動作周波数が上がると、このオーバーヘッドが無視できないものになってきた。

この問題に対する対策がTLBである。TLBは「PTE専用のキャッシュ」だ。格納されるのは「直前に利用されたPTE」のみであり、これを利用するのはAddress Translationのメカニズムのみである。

こちらも以前は1段のTLBで済んでいたのが、命令/データ用が分かれたうえ、最近では「2次TLB」もでてきた。これはOSが利用するメモリーの量が段々増えてきて、同時に利用されるPTEの数が増えてきた結果、TLBを増量しないとキャッシュが有効に効かなくなってきたためだ。だからといって、TLBのエントリを無闇に増やすと(1次キャッシュ同様に)TLBの検索そのものに時間が掛かるので、複数段構成にしようというわけだ。

ちなみにNehalem/WestmereベースのCore iシリーズの場合、その前のCore 2 Duo/Quadと比べると、TLBはちょっと複雑な構造になっている。

| Nehalem/Westmere | Core 2 Duo/Quad | |

|---|---|---|

| 1次命令TLB | 128エントリ/コア (64エントリ/スレッド) 4ウェイセットアソシエイティブ |

128エントリ 4ウェイセットアソシエイティブ |

| 1次データTLB | 64エントリ 4ウェイセットアソシエイティブ |

16エントリ 4ウェイセットアソシエイティブ +64エントリ 4ウェイセットアソシエイティブ |

| 2次TLB | 512エントリ 4ウェイセットアソシエイティブ |

なし |

利用する環境によって、必要とされるTLBの大きさは変わる。無尽蔵に大きなTLBを設ければ済む、というものではないことがおわかりいただけよう。ちなみにAMDの「K8」(Athlon 64)の場合、命令/データともに1次/2次TLBを持ち、さらに3次キャッシュが2次TLBとして動作できるような構造になっていた。今のNehalemコアのCore iシリーズなどよりも、遥かに大量のページを扱うことを想定した、非常にサーバー向けのアーキテクチャーと見ることもできよう。

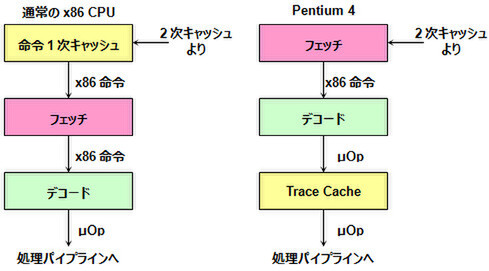

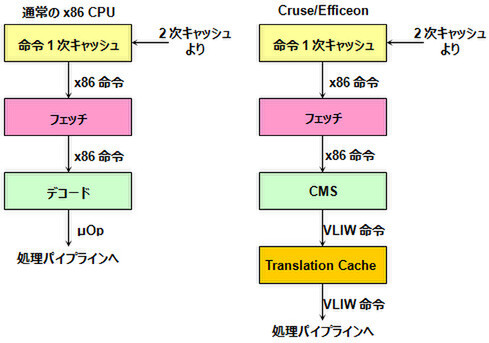

話を戻すと、このほかにx86系で使われた技術としては、「Pentium 4」の「トレースキャッシュ」(Trace Cache)と、Transmetaの「Crusoe」「Efficeon」で使われた「Translation Cache」が挙げられるが、これはどちらも似たものである。

Pentium 4のTrace Cacheは図2のように、パイプラインの構造を通常と変えて、デコード後の命令をキャッシュするようにしたものだ。これによりデコードの処理を実際の処理の流れから切り離すことに成功し、特にループ処理などで効果的に働くはずだった。しかし、肝心のPentium 4の処理性能の低さもあってその効果はほとんど評価されなかった。

ただ、インテルの内部ではこのTrace Cacheに一定の評価をしているようで、Nehalem/Westmereコアの「LSD」(Loop Stream Detector)を経て、まもなく登場する「SandyBridge」では、「Devoded μOps Cache」という形で、従来の1次キャッシュと並行して利用されることになる。

Crusoe/Efficeonもこれに似ている(図3)。これらは、x86をまず独自のVLIW命令に変換する(これをコードモーフィングと呼ぶ。詳細はこちらの記事を参照)。その際に、変換後のVLIW命令を一時的に蓄えるTranslation Cacheと呼ばれるものが存在した。

フェッチ/デコードをスケジューラー以降のパイプラインと分離して、間にキャッシュを挟むという方式は、x86に限らずほかのCPUアーキテクチャーでも見かける方式だ。しかし、以前は数命令分のバッファ程度、ということも多かった。ところが昨今では、性能改善のためにこのバッファを増やすケースが次第に増えてきている。将来的には、もっと多くのx86プロセッサーでも広く採用されていく可能性がある。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ