Intelチップセットの歴史 その5

次世代のIntel 6シリーズはDMIを高速化しUSB 3.0対応?

2010年01月19日 12時00分更新

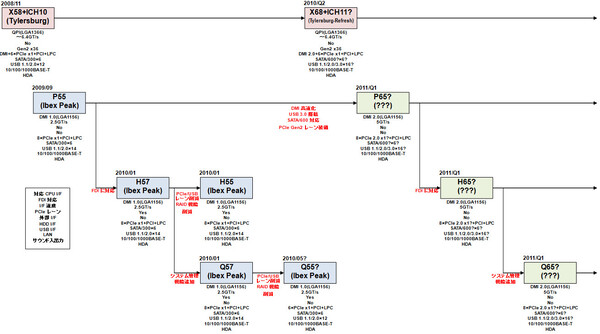

年末年始スペシャルを挟んでちょっと間が開いてしまったが、インテルのデスクトップ向けチップセットロードマップの最終回を始めよう。既報のとおり、1月8日にインテルは、CPUのClarkdaleとH57/H55/Q57の各チップセットを発表。これで“近日発表”予定だったチップセットはほぼ全部出揃った事になる。まずはこのあたりのおさらいから始めたい。

Lynnfield世代でICHはPCHに

機能の強化はわずか

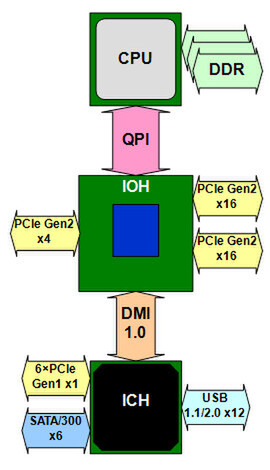

まず2008年11月に、Core i7シリーズの投入にあわせて登場したのが「Tylersburg」のコード名を持つ「Intel X58 Express」である。これは右図のような構造をとっている。

CPUのインターフェースそのものは、20bit幅のQPI(Quick Path Interconnect)になっており、これでIOH(I/O Hub)とつながる。IOHはPCI Express Gen2を最大36レーン出すことができ、ICHとは従来のDMI(Direct Media Interconnect)でつながる。CPU側にメモリーコントローラーが移動したため、IOHは事実上、PCI ExpressとQPI/DMIのブリッジとして動作するような形になっている。

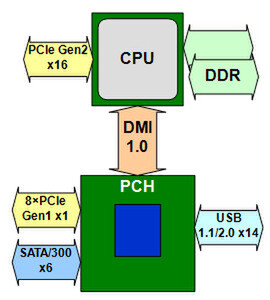

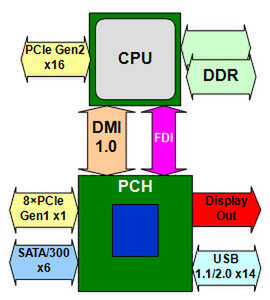

ただし、デスクトップ向けでQPIを持つCPUは、当初投入されたNehalemコアの「Core i7-9xx」シリーズのみ。続いて2009年9月に登場した「Lynnfield」ベースのCore i7/i5は、CPU側にメモリーコントローラーのみならず、PCI Expressのインターフェースも搭載。チップセットとの接続は、下図のようにDMIを使う形になっている。

そのため、事実上CPUに直接ICHが接続される構造になるが、製品差別化のためか、あえてICHではなく、「PCH」(Platform Controller Hub)と称している。

ちなみにPCHは、スペック的には「ICH10」よりも少し進化しており、強いて言うのであれば「ICH11相当」というところか。実のところICHのスペックは2006年登場の「ICH8」の世代から大きく変わっておらず、違いは以下の程度でしかない。

- PCI Express 1.1(Gen1) x1レーンの数

- USB 2.0/1.1ポートの数

- SATA 300ポートの数

PCHの場合、USBポート数は14でICH10と同じだが、PCI Express Gen1レーンが最大8本(ICH10は6本)取れるのが大きな違いといったところで、その意味でもICH11相当と言うわけだ(編注:インテルでは、ICH10以降PCI Express 2.0対応と称しているが、転送速度は2.5GT/秒に留まっており、厳密な意味ではこれは2.0ではない)。

最初のPCHである「Intel P55 Express」はほとんどICHと機能が変わらなかった。だが、続いて登場したH57/H55/Q57は、DMIに加えて「FDI」(Flexible Display Interface)と呼ばれるバスが追加されており、これが加わったことでICHと機能の差別化がされた。

2010年1月に登場した「Clarkdale」ベースの新しいCore i5/i3は、Lynnfieldと同じLGA1156ソケットに対応したパッケージながら、MCMの形でGPUコアをCPUパッケージ内に統合している。そのため、GPUからの映像出力を新たに追加する必要が出てきた。この映像出力を、FDIとしてDMIとは別に用意し、PCHの側に出力にあわせたPHY機能を搭載して、最終的にディスプレー出力している。

ちなみにFDIは、4対のDifferential Signalingで、2.7GT/秒の伝達速度を持つものと定義されている。FDIの信号(やピン配置)そのものはLynnfield/P55の世代から定義されているが、内蔵GPUをもたないLynnfieldや、FDIへの対応を行なわないP55の場合、このFDI信号は単に無視される。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ