拡張命令から見るx86 CPUの最終回は、拡張命令の今後について語ろう。とは言っても、ここで述べるのはあくまで現時点で見えているだけの話である。

Sandy Bridgeで新命令「AVX」が追加

Larrabee命令のx86導入はまだ先?

まず、本筋とあまり関係ない話を片付けておこう。インテルが現在「Larrabee」と呼ばれるGPU(というかStream Processor)を開発中なのは、すでに周知の事実だ。このLarrabeeでは、「LRBni」(Larrabee New Instructions)と呼ばれる新しい拡張命令が搭載されることがすでに明らかにされている。

LRBniに合わせて、32個の新しい512bitベクタレジスター「v0~v31」と、8つの16bitマスクレジスター「k0~k7」が追加され、(少なくとも)Vector Arithmetic/Logical/Shiftの命令が用意されることが明らかにされている。もっとも公開されているのはここまでで(詳細な命令セット情報やエミュレーション環境などは、機密保持契約を結ばないと入手できない)、また、短期的にはLRBniを実装するのはLarrabee(とその後継製品)のみとされているから、直接x86 CPUとどうこうという話ではない。

ただし、インテル社のCTO(最高技術責任者)であるジャスティン・ラトナー(Justin R.Rattner)氏は、長期的にはLRBniかその将来バージョンが、将来のIAコアの一般的な拡張命令として搭載される「可能性はある」としており、将来的にはこうしたものも入ってくるかもしれない。

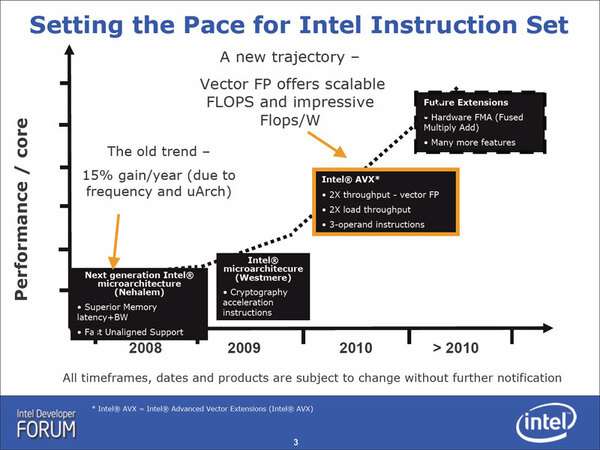

では本筋に入ろう。インテルは現在、NehalemコアCPUを45nmで製造中だが、これを32nmプロセスに移行させた「Westmere」を2010年に導入する。このWestmereでは、命令セットについては暗号化アクセラレーションが若干拡張される程度だ。だが、これに続く同じ32nmで製造される次世代アーキテクチャーの「Sandy Bridge」に、「AVX」(Intel Advanced Vector eXtentions)と呼ばれる新しい拡張命令が搭載されることが明らかにされたのは、2008年3月に上海で開催されたIDF Shanghai 2008のことだ(関連記事)。冒頭のスライド画像はその時のものだ。

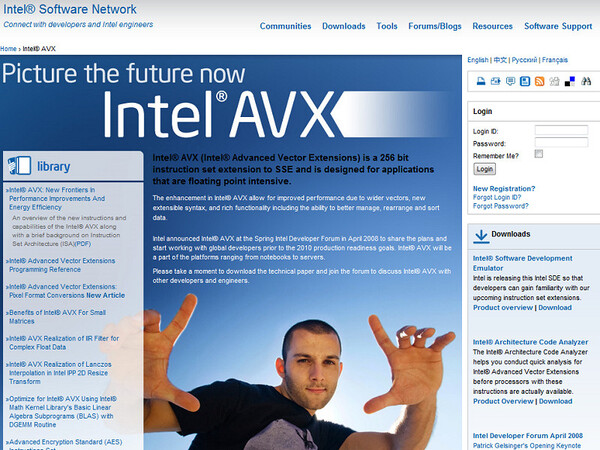

この発表時は概略程度で、あまり突っ込んだ中身は公開されなかったが、その後次々とドキュメントなどが提供されており、現在AVXのページでは仕様だけでなく、さまざまな応用事例をまとめたアプリケーションノートやAVXのソフトウェアエミュレーター、コードアナライザーなどが入手できるようになっている。

余談だが、このあたりは、AMDがx86-64を公開した時に非常によく似ている。やはり仕様書のみならず、ソフトウェアエミュレーターやコードアナライザー、アプリケーションノートなどが、実際のプロセッサーが提供されるはるかに前から提供されていた。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ