ロードマップでわかる!当世プロセッサー事情 第796回

Metaが自社開発したAI推論用アクセラレーターMTIA v2 Hot Chips 2024で注目を浴びたオモシロCPU

2024年11月04日 12時00分更新

MTIA v2で性能は3倍に向上したが

チップサイズと消費電力も跳ね上がる

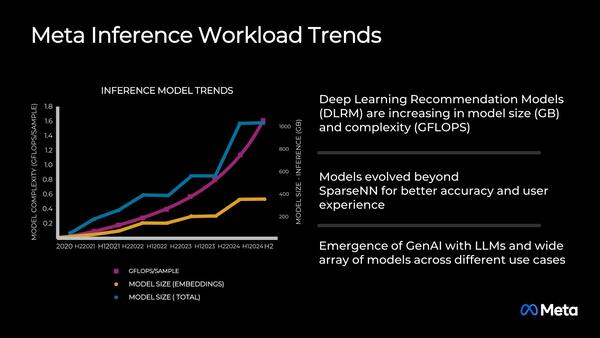

ここから本題のMTIA v2に話を移す。2020年のMTIA v1の設計開始時点から比較すると、Meta社内で利用されているモデルのサイズも複雑さも大幅に増している。

モデルのサイズと複雑さが大幅に増している。これは比較的理解しやすい話である。Recommendation一つ取っても、より良い結果を得るためにはより複雑なモデルが必要とされ、必然的に容量も複雑さも増えることになる

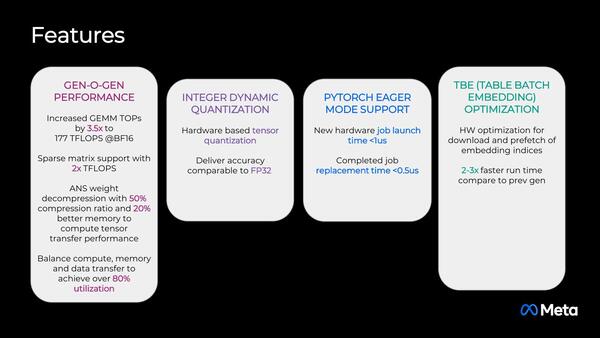

そこでMTIA v2の設計目標は下の画像のように設定された。結果として完成したのがその下の画像だ。

MTIA v2の設計目標。ピーク性能を追い求めるのではなく、たとえばある処理をスタートするのに1μs未満、完了した処理の後始末は0.5μs未満、といった実用的な目標が掲げられているあたりは、自社向けプロセッサーらしい感じが強い

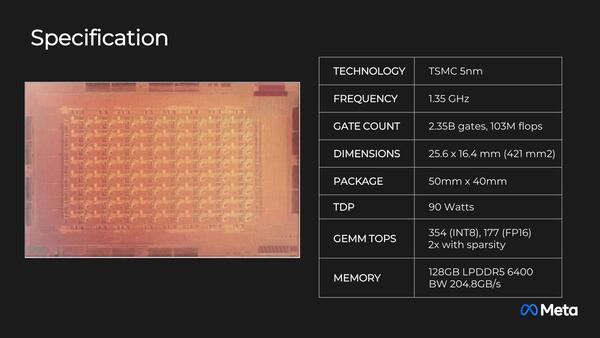

TSMC N5を使いつつ、ダイサイズは421mm2とかなり大規模化している。TDPも90Wまで引き上げられた。おもしろいのは外部接続のメモリーが引き続き128GB LPDDR5-6400になっていることで、帯域は204.8GB/秒のままである。消費電力などの観点から引き上げられなかったのか、それともv1以上の容量/帯域は不要と判断されたのかは不明である。

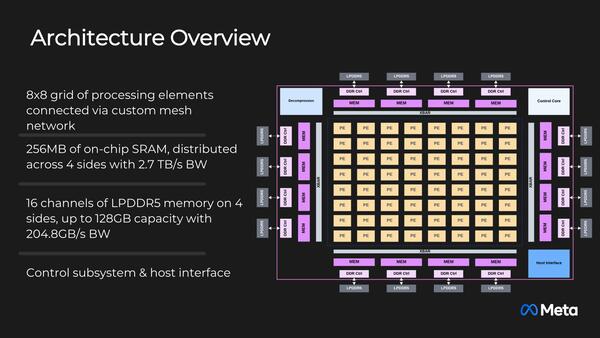

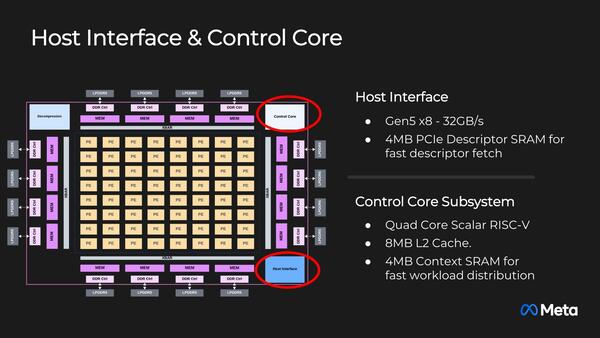

内部構造そのものは以前と非常に似ている。オンチップSRAMの容量は128MB→256MBに増強された。I/FもPCIe 5.0×8に強化され、またコントローラーもけっこう強力になっている。それとv1では基本的にメッシュネットワーク構成だったのが、v2ではNoCに切り替わった。

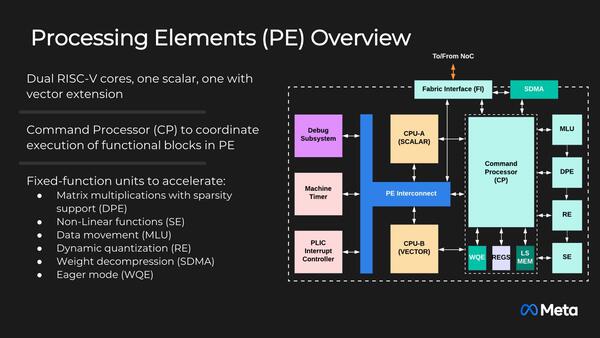

個々のCPの中身が下の画像だ。Vector付きのRISC-VコアとVectorなしのRISC-Vコアが搭載されるのは同じだが、それとは別にコマンドプロセッサーが搭載され(たのか、実はMTIA v1のPEにもあったのかは判断つかないが)、これが行列演算(DPE)や非線形関数(SE)などをまとめて管理する。

この連載の記事

-

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 - この連載の一覧へ