先週の続きで今週もRISC-Vの話をするつもりだったのだが、SC23がコロラド州デンバーで開催され、これにあわせてTOP500のリストも更新された。ということで長らく懸案になっていたAuroraがついにランクインしたため、急遽予定を変更してこちらを解説する。

AuroraはTop500のランキング2位

トップを維持したFrontierの半分の性能

Auroraは今年5月に行なわれたISC 23のタイミングでは、スパコン性能ランキングとなるTOP500にまだエントリーしなかったという話は連載723回で説明したとおりである。今回はきちんとエントリーされたので、分析の前にまずは結果から伝えよう。

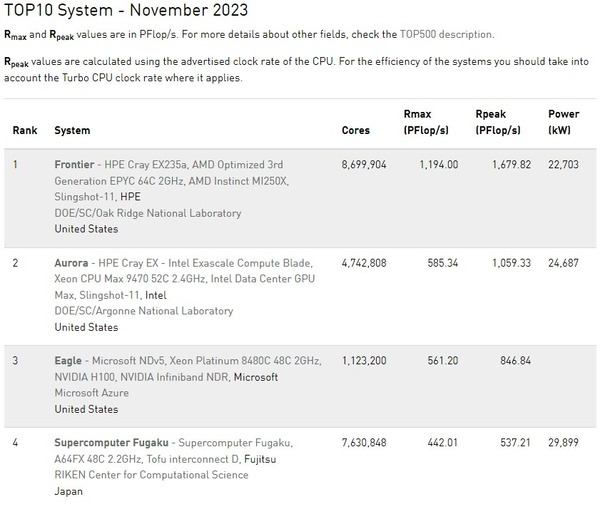

そのAuroraであるが、ランキング2位である。下の画像はTop 4までの抜粋であるが、ラフに言ってトップを維持したFrontierの半分の性能しかない。それでもやはり今回新規にランクインしたマイクロソフトのEagleを上回る数字だし、富嶽の性能は抜いているので、それなりに面目は立ったと言えなくもないが、いろいろな意味で問題がありすぎる。

ちなみにこの585.34PFlopsという数字、Ian Cutress博士によれば「システムの半分を稼働させている」のだそうだ。後で数字を検討するが、コア数やRpeak(理論性能)が明らかに所定のものと異なっている。したがって、フルシステムではもう少し性能があがり、1170PFlops程度になるものと思われる。それでもFrontierには届かないのだが。

Aurora isn't #1. The PF for power isn't good. This int a full system run, I think he said half with little optimization. Still expecting 2EF when full #Top500#SC23#iamhpcpic.twitter.com/BOW4sXwylc

— 𝐷𝑟. 𝐼𝑎𝑛 𝐶𝑢𝑡𝑟𝑒𝑠𝑠 (@IanCutress) November 13, 2023

さて、インテルはプレスリリースで第2位になったことをアピールしているが、控えめに言っても結果は大惨事である。具体的に言えば以下のとおり、もうなにから手を付けて良いのか、という感じではある。

(1) 7月の時点で75%の機材が最終構成に合わせて更新されたにもかかわらず、いまだにフルシステムでの稼働ができていない。

(2) 半分のシステムにもかかわらず、この時点で消費電力は24.6MWに達している。

(3) 半分のシステムで理論性能は1059.33PFlopsなのに、実効性能はたったの585.34PFlopsに過ぎない。

この連載の記事

-

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 - この連載の一覧へ