3D V-Cacheを搭載した

Genoa-X

次いでGenoa-Xであるが、こちらはGenoaに3D V-Cacheを搭載したモデルである。3D V-CacheをEPYCに搭載した場合の効果というのは連載642回のMilan-Xの時にも説明した通りだ。

当たり前だがなんでも性能が上がるというわけではなくキャッシュ増量の効果が得られるアプリケーションに限るし、また構成的にも増量したキャッシュがうまく使えるようなケースに限られるが、そうした条件をうまく満たすと大幅に性能が上がることがわかっている。

これは今回のGenoa-Xにもそのまま当てはまる。まずSKUであるが、下の画像の3製品のみである。

96コアのEPYC 9684XのみTDPがやや高いのはわかるが、400Wというのは驚き。スペック的にはEPYC 9654と大きくは変わらない(Baseが2.4GHz→2.55GHzとやや高い)のに、なぜ40W多いのか? EPYC 9684X以外は8ダイ構成である

ちなみにEPYC 9684X、最大ブーストは3.7GHzでEPYC 9654と変わらないが、全コアブーストは3.42GHzとやや刻んできており、EPYC 9654の3.55GHzよりやや低めである。

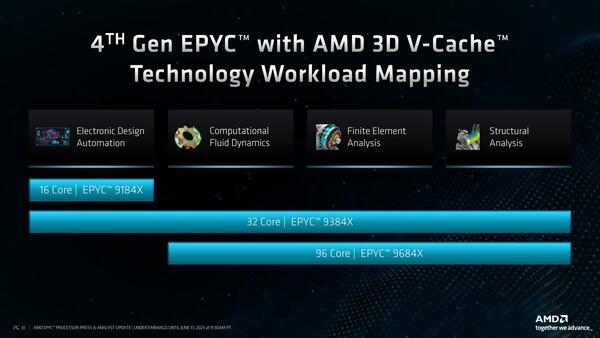

それぞれのラインナップの用途をまとめたのが下の画像で、EDA向けなどにはスレッドあたりの性能が高いことが求められるので16コアのEPYC 9184Xが最適だが、CFDやFEA、構造計算などはトータルの性能が求められるので32コアのEPYC 9384Xや96コアのEPYC 9684Xが向いているという説明である。

ちなみにEPYC 9684Xではコアあたり12MBの3次キャッシュが利用できるわけだが、EPYC 9384Xで24MB、EPYC 9184Xでは48MBの3次キャッシュが利用できることになる。

加えて言えば全製品ともDDR5-4800 12chをサポートしているわけで、スレッドあたりのメモリー帯域やキャッシュ容量が問題になる場合は、必ずしも96コアのEPYC 9684Xではなくより下位モデルの方がトータルでは性能が高いということもあり得るわけで、このあたりはアプリケーション要件に応じて選べばよいという姿勢である。

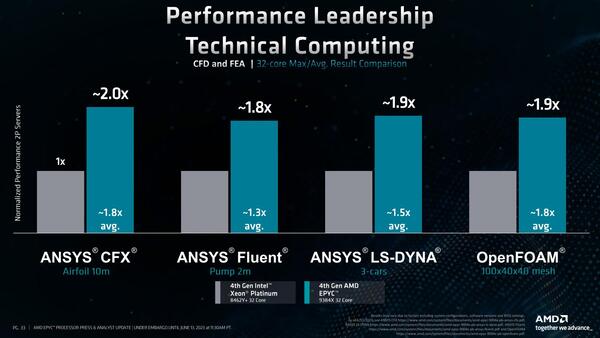

実際に、Sapphire Rapidsとの性能比較が下の画像だが、これも当然条件次第なところがある。

なおマイクロソフトは今回も、Genoa-Xを実装したHBv4 Instanceの性能を開示している。今回は分析はしないが、結果から言えば以前のMilan-Xの時のように、なんでもかんでも性能が上がるわけではないが、うまくスイートスポットにはまれば(Genoaと比較しても)性能が向上することが示されている。

マイクロソフトはこのHBv4 Instance、当初はGenoaベースでプレビューを提供していたが、今後すべてをGenoa-Xに更新の上で正式にサービスを提供する予定である。

この連載の記事

-

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 - この連載の一覧へ