RISC-Vコアが外部メモリーを参照せずに処理できる範囲に

ネットワークの大きさに留める

では低消費電力をどうやって実現したのかを説明しよう。GAP8のベースになるのは、2013年にスタートしたPLUPプロジェクトだ。これはRISC-Vベースのオープンソースなハードウェアを構築するというもので、IoTからHPCまでさまざまな用途に向けたRISC-Vコアとその周辺回路、さらにはソフトウェアまで手がけるものである。

PULP(Parallel Ultra Low Power)プロジェクtpは、チューリッヒ工科大のIIS(Integrated Systems Laboratory)とボローニャ大のEEES(Energy-efficient Embedded Systems)グループが共同で始めたものである

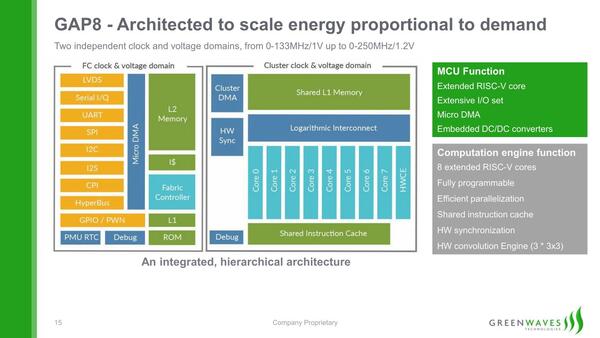

このPULPプロジェクトで提供されるCV32E40P(かつてはRIS5Yと呼ばれていた)コアを9つ統合したものである。

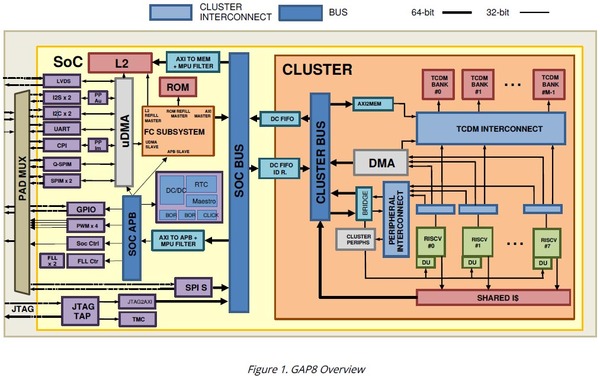

もう少し詳細な構造図が下の画像だ。個々のコアはいずれもRV32ICM(整数演算、縮小命令、乗徐算)をサポートした32bit RISC-Vコアである。CV32E40Pはパイプライン段数4段のインオーダーの構成で、効率はともかくとして絶対性能はそれほど高くない。

もちろん上の画像にもあるように、FC(Fabric Controller)側に512KBの2次キャッシュが搭載され、またクラスターの側には16KBのTCDM(Tightly-Coupled Data Memory)がファブリック経由で複数個搭載されている。

クラスター側のコアはTCDMで処理をして、このバックアップとしてFC側の2次キャッシュが利用される格好だ。命令キャッシュとしてはFC側に1KB、クラスター側に4KBが用意されている。

アプリケーションプロセッサーだとしたらこれはかなり少ない方だが、32bitのMCUコアであればこれで十分であろう。ちなみに、SoCの外にHyperBusと呼ばれるI/Fを利用して、SRAMないしフラッシュメモリーを外部に搭載することもできる。

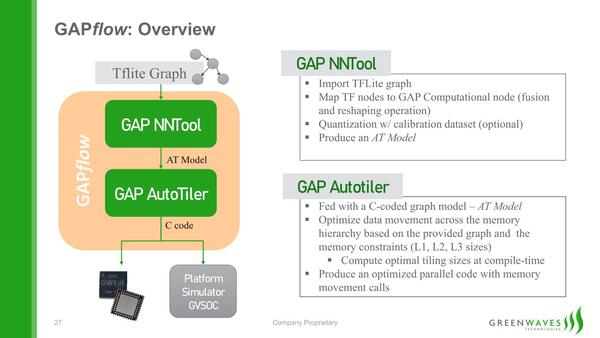

ただこれだけ見ても、なぜこれでAIの推論が高効率に行なえるのかさっぱりわからないだろう。この鍵を握るのが、GreenwavesのGAPflowというソフトウェアである。GAPflowは大きく2つのツールからなる。

最初のGAP NNToolは純粋にTensorFlow Liteのグラフを読み込み、これを続くGAP AutoTiler(AT)用に独自フォーマットに変換する。この際に量子化(Quantization)を可能なら事前に行なうことで処理負荷を減らす形だ。これそのものは珍しくない。

続くGAP AutoTilerがグラフを分割し、8つのタイル(=8つのRISC-Vコア)が外部メモリーを参照せずに処理できるようなサイズに落とし込むことで、個々のタイルはTCDMだけを参照しながら処理するようになる。

当然外部メモリーの参照が必要なければ処理は高効率に行なえるし、そもそもTensorFlow Liteを利用している時点で巨大なネットワークを動かすことはあり得ないので、メモリーが足りなくなるようなケースもない、というわけだ。

おそらく巨大なネットワークを動かそうとすると、AutoTileをかけた時点でエラーが出て、もっと小さなネットワークにするように勧告されることになるだろう。

その意味ではあくまでエンドポイントAI向けのプロセッサーコアに最適化されていると言えなくもないが、無理に巨大なネットワークを動作させるためにアクセラレーターや外部エンジンなどを突っ込み、複雑な構成になって消費電力やダイサイズが肥大化し、最終的なコストを引き上げてしまうより、RISC-Vコア+HWCE(Hardware Convolution Engine)で収まる範囲にネットワークの大きさを留めさせることで、低コストでエンドポイントAIが実行できるようにするという同社の設計方針は、わりと考えさせるものがある。

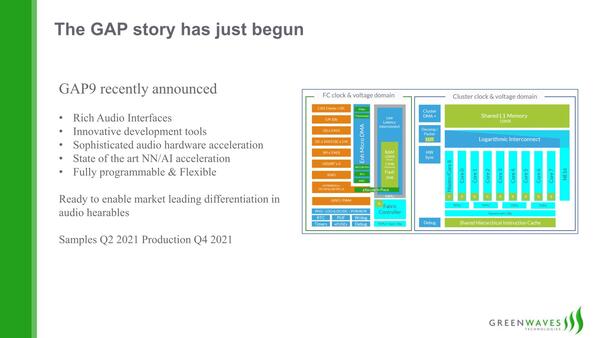

Greenwavesはこれに続き、オーディオインターフェースを搭載したGAP9をすでに発表済みである。

この画像では2021年に量産とされているが、現時点ではまだチップが完成していないようだ。ただすでに設計そのものは終わっているようで、GAP9 StoreではeFused(1回書き込みのみのFPGAのようなデバイス)を利用した評価キットが、契約ユーザー向けに出荷可能になっている。

うまくターゲットを絞れば、複雑なメカニズムや突拍子もないアーキテクチャーを使わなくてもAIプロセッサーは実現できる、という良い例かもしれない。

2022年11月9日追記

Greenwaves Technologies社よりGAP9の現状についての連絡をいただいた。それによれば2022年3月からチップを実装した評価用キットを顧客に提供中で、すでに量産ウェハーも上がってきており、これを利用したGAP9のWL-CSPチップの出荷も開始しているとのこと。すでに量産シリコンの品質検証も完了し、2023年第1四半期から出荷予定とのことである。以上、お詫びして訂正する。

※編注:次回の連載記事は、都合により14日23時に掲載予定です。通常より約半日掲載が遅くなりますことをご了承下さい。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ