AMDやNVIDIAのGPUに近い内部構造

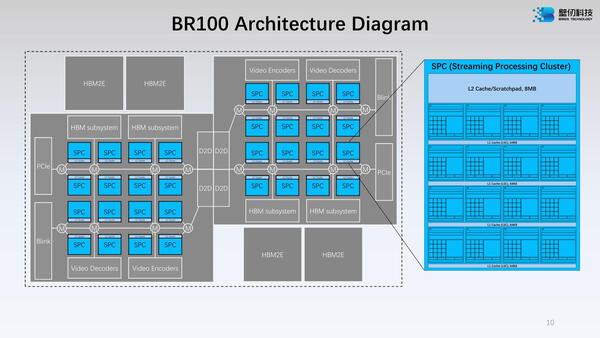

さてそのBR100の内部構造が下の画像だ。それぞれのダイには16個のSPC(Streaming Processing Cluster)が搭載され、それとは別にHBM2eのI/F×2とPCIe I/F、BLink I/F、そしてなぜかビデオエンコーダー/デコーダーが搭載されている。

BR100の内部構造。L2の“Build-in reduction engine”に関しては最後のスライドで説明する。またSPCの内部のEUの数は4/8/16と変更できるらしい(動的に、という意味ではなく将来は下位グレードの製品を作り分けられる、という意味)

今回このエンコーダー/デコーダーの詳細は公開されていないが、製品ページによれば1ダイのBR104は32ch H.264/HEVCエンコーダーと256ch H.264/HEVCデコーダー(どちらもFHD@30fps)、2ダイのBR104はそれぞれ64ch/512chとなっている。それなりに強力には見えるが、4K@30fps相当で考えればBR104が8ch/64ch、BR100が16ch/128chという計算で、コンテンツ配信ネットワーク向けにはもう少し性能が欲しい感じもする。

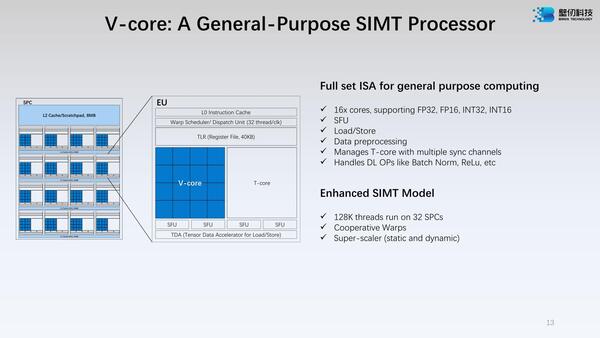

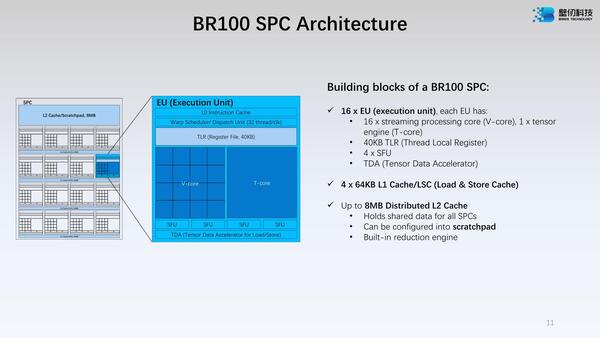

話を本体に戻すと、個々のSPCの内部には16個のEUが含まれている。個々のEUには16個のV-Coreと1個のT-Coreが含まれている格好だ。V-Coreは通常のVectorというかSIMD演算ユニット、T-CoreはMatrix演算ユニットに相当すると考えるのが正しいところだろう。

ただ演算はSIMDというよりはSIMT的な動作のようで、複数のスレッドをWarpという単位で管理しているあたりは、AMDやNVIDIAのGPUに近いと言える。ちなみにT-Coreとは別にTDA(Tensor Data Accelerator)が搭載される。

あと、1つのSPC(=16EU)ごとに8MBの2次キャッシュが搭載されるとしている。ということは、ダイ全体で言えば128MBの2次キャッシュが搭載されている格好で、これはかなり巨大である。

個々のV-Coreの説明が下の画像だ。といっても概念的な部分であって、肝心の演算ユニットの詳細などは明らかにされていない。やや意外だったのは、V-CoreはINT 8をサポートしないことで、INT16/32とFP16/32のサポートのみである。また32SPCで最大128Kスレッドをサポートというのもすごい数字であって、つまり1個のSPCあたり4Kスレッドを扱えるという話である。

TLR(Thread Local Register)の40Kは、普通に考えると十分なのだが、1つのEUで4Kスレッドを扱うことを考えると、もう少し大きくても良いような気もする。多少大きくしたところでスレッドの入れ替えが煩雑に行なわれると結局TLRの入れ替えも煩雑にならざるを得ないから、割り切ったのかもしれない

1 Warpがどの程度のスレッドを扱えるのか不明だが、普通に考えればEUの数に合わせるのが妥当で1 Warp=16スレッドということになるのだが、実は後述するように32スレッドになっている。

ということは128個のWarpを1つのEUでハンドリングできることになるのだが、少しこれは多くないだろうか? という気もしなくはない。またV-Coreはスタティック及びダイナミックなスーパースカラーを実装、というのも不思議な部分だ。

スタティックの方はともかく、ダイナミックなスーパースカラーといっても、そもそもスーパースカラー的になにを動かすのか? が今1つわからない 。

可能性としてあるのは、下の画像を見るとLSU(Load/Store Unit)が存在していない。思うに個々のV-CoreにはINT/FPの演算ユニットとLSUがそれぞれ搭載しており、この演算ユニットとLSUが個別に動作可能なのでスーパースカラーと言っているような気がする。

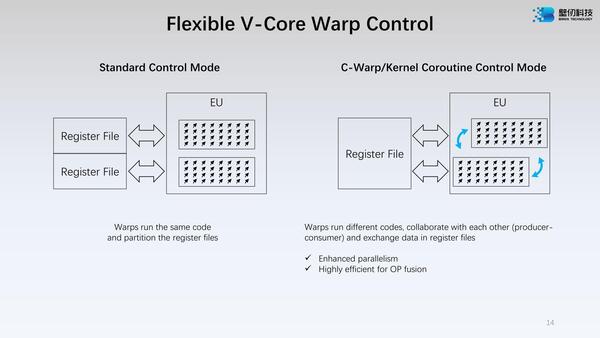

ちなみにこのWarp、必要に応じて中でダイナミックに動作を切り替えられるとしている。下図右側の構成は珍しいというか、プログラミングの難易度が上がりそうな気がする。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ