初のPNPベースのプロセッサー

Enviseが誕生

このPNPの概念をLightmatterが発表したのは2019年のことであるが、そのLightmatterは今年3月に、Enviseと呼ばれる初のPNPベースのプロセッサーを発表した。

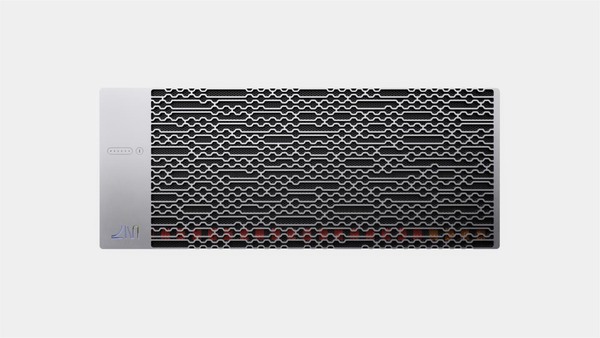

Enviseの外観は「電源端子が4つ?」に見えるが、これを拡大してみると、16レーン(?)の光出力が4組用意されているようだ。

内部構造であるが、これが今ひとつわからない。と言うのは、“Inside the chip”で示されたのが下の2つの画像である。

察するに、Enviseは2層構造になっており、下層がいわゆるCMOSベースのチップで、その上にPNPが搭載される格好になっているのだろう。

なぜCMOSが下層か? というと、パッケージ裏面からBGAの形で信号を引っ張りだすとしたら、間にSilicon Photonicsを利用したPNP層が挟まっているのは、配線取り回しでいろいろと不都合が多い。したがって最終的なパッケージは、CMOS層の上にPNP層が載っていると考えるのが自然だ。

ただそれをまとめて製造しているのか、それともCMOS層とPNP層を別々に製造して、後工程で張り合わせているのかは不明である。現時点では張り合わせているように思う。

作り方はともかくとして、まず下の画像のPNP層の方だが、こちらは32個のRISCコアと500MBのSRAM、それとGraph Processor(グラフ処理をここで行なうのだろう)とPhotonic Tensorcore Controlユニット、あとはPCIeとFabric(Enviseは複数チップで連動させることが可能で、その際の外部I/FがこのFabricに当たる部分だろう)から構成される。

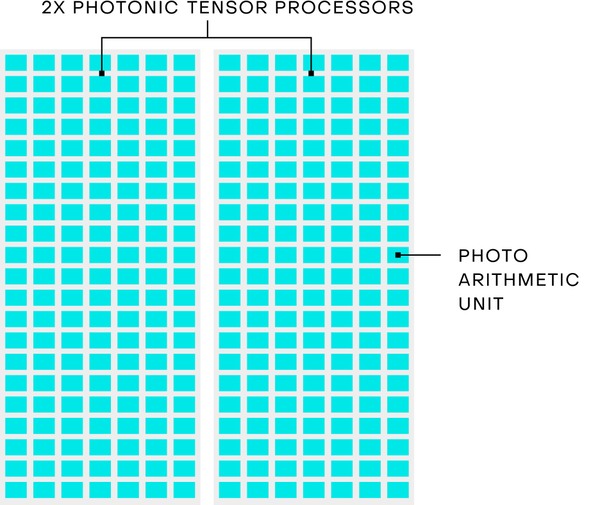

おそらくPhotonic Tensorcore ControlはPNPの制御部分のロジックで、ここにはTSVも搭載されており、そのTSVでPNP層と接続するものと思われる。一方のPNP層の方、こちらは147個のMZI(LightmatterではこれをPhoto Arithmetic Unitと呼んでいるが、MZIだけなのか、他になにか入っているのかは不明)が2組用意される。

中央に隙間があるのは、ちょうどこの下にCMOS部のPhotonic Tensorcore Controlが位置する格好になっており、ここから制御信号がTSV経由で渡されてPhotonic Tensorcore Controlに分配される格好なのだろう。

LightmatterはこのEnviseをチップ単体売りではなく、システム売りの形で提供することを想定している。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ