RISC-VはSIMD演算ではなくベクトル演算

違いはレジスター長が固定かどうか

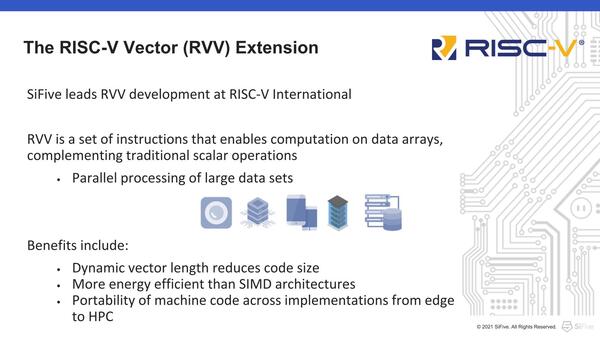

では、RISC-Vをどうやって実装したか、というのが今回の話だ。もともとRISC-VではRVV(ベクトル拡張)についてずっと議論が進んでいた。議論が進んでいたというか、いろいろ揉めていたというのかは微妙なところであるが、2019年6月にはv0.7.1がリリースされており、ところがv1.0で仕様が固定(Frozen)されたのは2021年9月、というあたりからけっこう議論が錯綜したのがわかる。

この仕様策定までの期間がどうしても長くなるのがRISC-Vみたいな仕様をオープンな場で議論する方式の欠点ではあるのだが、それはともかく。

RISC-Vの場合、SIMDではなくベクトルとされている。最大の違いはレジスター長が決め打ちでないことだ。例えばx86系で言えば、1つの演算で処理できる最大のサイズはMMX/3DNowが64bit、SSEが128bit、AVX2が256bit、AVX512が512bitと決められている。要するに1回の命令で処理できるSIMDレジスターは1つであり、1024bit分のデータを処理したければMMX/3DNowで16回、SSEで8回、AVX2で4回、AVX512でも2回命令を発行する必要がある。

これに対してベクトルの方は、1つの命令で処理できるデータ量が固定長ではない。したがってEsperantoのET-Minionのように、それこそ最大で512回の演算を処理できるようなものも登場してくる。ET-MinionはRVVとは異なる独自実装であるが、RVVも基本的なアイディアは同じであり、実際のベクトルレジスターよりも長いデータを取り扱える。ArmのSVE(Scalable Vector Extention)や、最近登場したSVE2も考え方はよく似ている。

RVVそのものは、SIMD演算と同じく大量の数値演算に向けた拡張であって、必ずしもAI/機械学習向けではない。

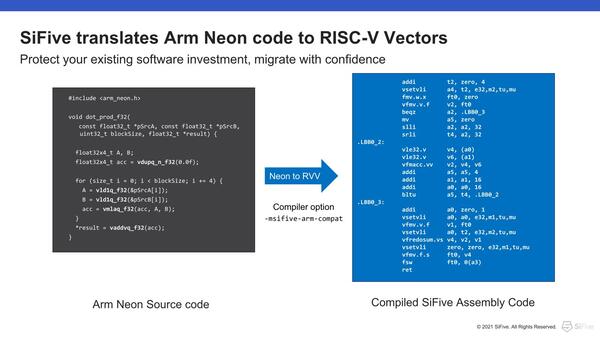

むしろ直接的なターゲットはArmということもあり、Armの64bit SIMD命令であるNEONを利用したアプリケーションを、簡単にRVVに移行できることをアピールしていたりする。

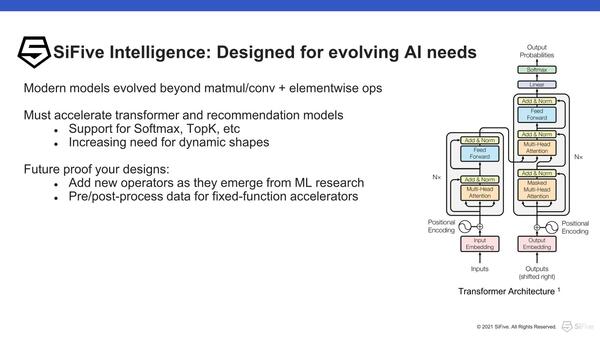

さて本題のAI向けの話だ。SiFiveはAI/機械学習向けにSiFive Intelligenceと呼ばれるソフトウェアとハードウェア(IP)のパッケージを提供している。

これまでは、例えば畳み込みを高速に処理するアクセラレーターだったり、もっとプリミティブに乗加算を高速に行なうハードウェアを入れたり、といった形でAIに対応と称することが多いが、同社はもう一歩先の、例えばTransformer(2017年に発表された多層ニューラルネットワークのモデルで主に自然言語処理に利用されている)や、いわゆるRecommendationなどに利用されるモデルは通常の畳み込みニューラルネットワークよりももっと複雑であり、こうしたモデルをより高速に実行できるように工夫しているのが特徴だ。

右の図はTransformerモデルのアーキテクチャー。2017年にGoogleのAshish Vaswani氏らによって発表された“Attention Is All You Need”という論文の中で示されているものである

もちろんこれはRVVの範疇ではカバーできないので、SiFiveはカスタム命令拡張(RISC-Vでは独自に命令を拡張することを許しており、SiFiveもこれを利用した形)を使って独自のAI処理命令を追加して、こうした複雑なモデルへの対応を行なっている。こうしたモデルでも、従来の乗加算や畳み込みの作業がなくなったわけではないので、こうしたものはRVVを利用して処理する格好だ。

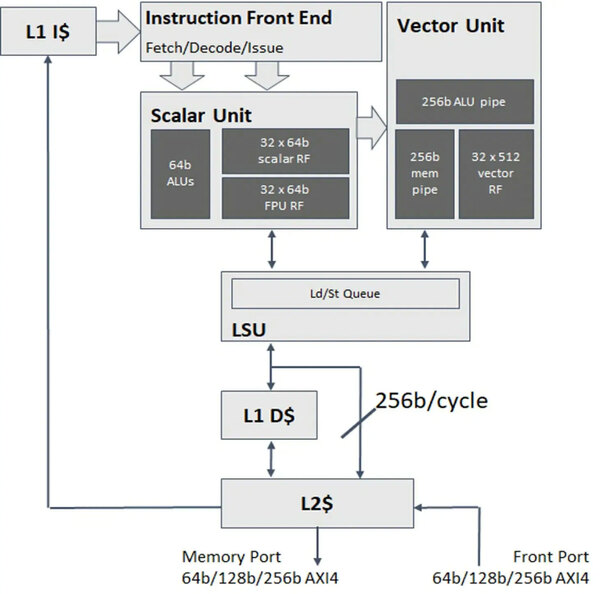

冒頭に書いたX280は、このSiFive Intelligenceを最初に実装したプロセッサーIPである。ベースとなるのは同社のU74という、インオーダー構成ながら2命令の同時実行が可能なパイプライン8段のプロセッサーで、SiFiveによればCortex-A55と同等以上の性能を持つとするプロセッサーである。x86で言うなら、Atom系列に相当すると考えればいい。

このU74コアに、256bit幅のベクトル演算ユニット(ただしベクトルレジスターは512bit幅)を組み合わせる形でRVVを搭載している。これにあわせ、ベクトル利用時は1次データキャッシュをバイパスして2次キャッシュに対して直接256bit/サイクルでのアクセスが可能な仕組みを追加したのがX280というわけだ。

またRVVはFP32/FP64以外にBF16/FP16やINT 8/16/32/64のデータ型をサポートしており、AIなどで多用されるINT 8/BF16/FP16を利用しての高速化が可能という形になっている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ