前回に引き続きインテル新製品の詳細をお伝えしよう。今回はSapphire Rapidsについてだ。さて、Intel Architecture DayとHotChipsでは「ほとんど」同じ内容であった。異なるのは後述するSVMとS-IOV周りの話だけである。ということで、主にArchitecture Dayのスライドを使いながら説明したい。

マルチチップで性能を向上させる

Sapphire Rapids

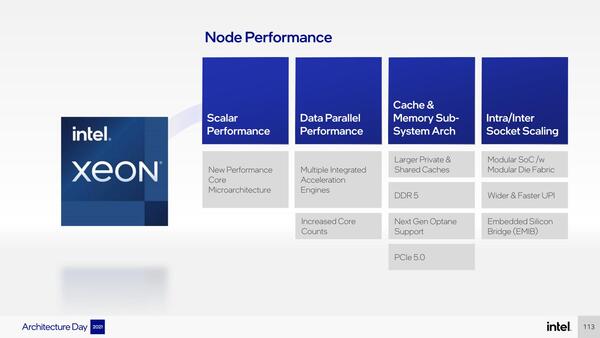

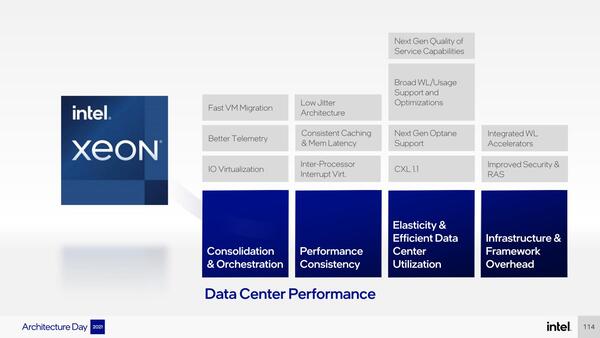

Sapphire Rapidsの設計目標は、ノードパフォーマンスとデータセンターパフォーマンスの両方を高めることとされる。具体的にはIPCを高めるとともに、これを支える周辺回路の強化を施すのがノードパフォーマンス、スケールアップ/スケールアウトサーバー構築の手助けとなる仕組みを導入することで、システム全体の実効性能を引き上げようというのがデータセンターパフォーマンスとなる。

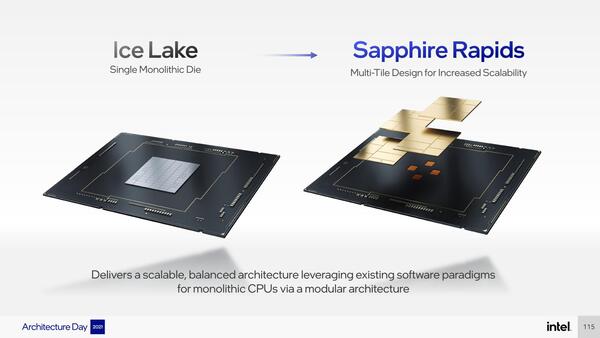

さて実現方法であるが、連載629回でも解説したようにマルチチップ(インテル用語ではMulti Tile)構成での提供となった。

さすがにインテルとしても、Xeon向けに巨大なダイを作り続けるというのはそろそろ限界に達したらしい。もっと正確に言えば、巨大なモノシリックダイの限界値はおおむね700mm2かそこらになる。これはどういう話かといえば、半導体製造におけるステッパーによる露光のフェーズで、マスクサイズの限界というものが存在するからで、これがおおむね600~700mm2(これは利用するプロセスやステッパーの性能に依存する)になる。

わかりやすい例が連載572回で紹介したCelebras SystemのWSEである。ダイそのものは4万6225mm2となっているが、写真を見ていただくとわかるように内部はこれを12×7で84個のタイルに分割しており、タイルあたりの面積は550.3mm2かそこらになる。

このチップの作り方は連載572回の3ページ目で説明したように、一度84個のタイルをバラバラにした後で、改めて間に配線を入れる格好でつなぎ合わせており、その意味ではモノリシックなダイとは言えない。

今回このSapphire Rapidsのタイルの面積は400mm2前後とされており、つまり4つでは1600mm2に達する。これをモノリシックで作る方法は現実問題として存在しない。したがって、よりコア数やキャッシュ、搭載するアクセラレーターなどを増やしたり、コアそのものを強化する(=コアのエリアサイズが増える)場合、マルチタイル方式は必須というか避けられない選択肢だったと言える。

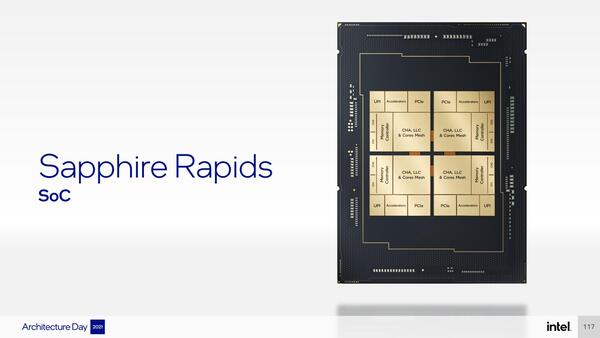

構成は下の画像にあるように、4つの同じタイルが載る構成であり、それぞれのタイルにコアとLLC、メモリーコントローラー、UPI、PCIe/CXL、アクセラレーターが載り、間がLink(筆者はこれはUPIベースだと思うのだが、インテルはこの方式を細かく説明していない)でつながれるという方式である。

要するにAMDの第1世代EPYCと同じ仕組みである。AMDは第2世代EPYCでコアとI/Oを分離する方式に改めたが、インテルが今後どういう方向性になるかは少し興味ある部分だ。

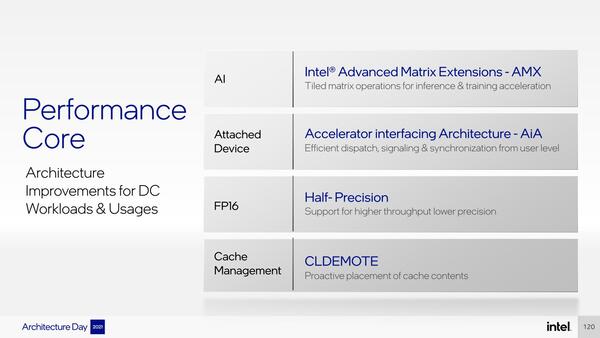

さて、Sapphire Rapidsのコアそのもので言えば前回説明したAlder LakeのP-Coreと同じものである。ただ前回の最後で説明したように、Sapphire Rapids向けは以下の違いがある。

- 2次キャッシュが2MB

- AVX-512およびAMXが利用可能

これ以外にも細かな違いがある。このうちAMXについては連載629回で説明済なので割愛する。AVX512に関しては、今年6月にAVX512-FP16の仕様がリリースされており、これに基づく形で実装されている。

AiAはこの後説明するが、アクセラレーター向けI/Fを新たに用意した、という話である。ただ、これは内部デバイスのみなのか、CXL経由で外部のアクセラレーターもサポートするのかは現時点では不明だ。なんとなくCXL経由もサポートしていそうだ

要するに従来のAVX512では、FP32だと最大で16演算/サイクルが可能だったのに対し、AVX5412-FP16だと32演算/サイクルが可能になるというわけだ。16bit演算に関しては、Cooper LakeにはBF16のサポートが追加されているが、FP16に関してはSapphire Rapidsが最初である。

CLDEMOTE命令は、実はTremontで最初に実装されている、というか実は筆者も最初このことを忘れていた。このCLDEMOTE命令、正式名称は“Cache Line Demote”命令で、オペランドで指定したアドレスを含むCache Lineを、プロセッサーコアに近いキャッシュ(つまり1次データキャッシュあるいは2次キャッシュ)から遠いキャッシュ(2次あるいは3次キャッシュ)に移動すべき、とプロセッサーに「示唆する」(Hint to)命令である。

即座に1次キャッシュなり2次キャッシュから排除するのではなく、次にプロセッサーが1次データキャッシュなり2次キャッシュの入れ替えをする際に、真っ先に2次/3次キャッシュにスワップアウトされるべき領域をプロセッサーに指示するという仕組みだ。

これは特にプロセッサー間の通信で効果的である。P-Core/E-Coreともに、2次/3次キャッシュはExclusive Cache(排他的キャッシュ)の形で実装される。したがって、あるコアがメモリーを書き換えた(この時点ではまだ1次キャッシュに保存されているだけである)後、そのアドレスをCLDEMOTE命令で3次キャッシュにライトバックさせると、他のコアがその内容を迅速に参照できるわけだ。

おそらくはE-CoreにもこのCLDEMOTE命令は実装されていると思われるが、説明によればAlder LakeではCLDEMOTE命令は無効化されているということで、現時点ではSapphire Rapidsのみが利用できることになる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ