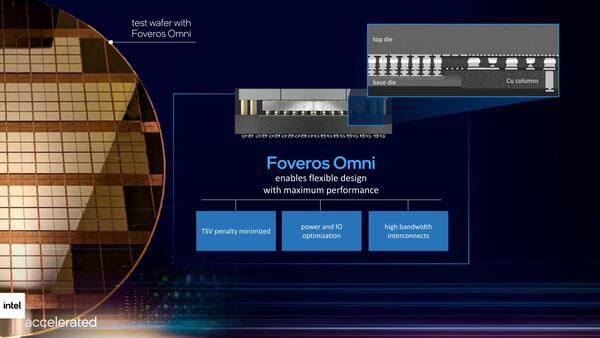

Foverosの新技術となるFoveros Omni

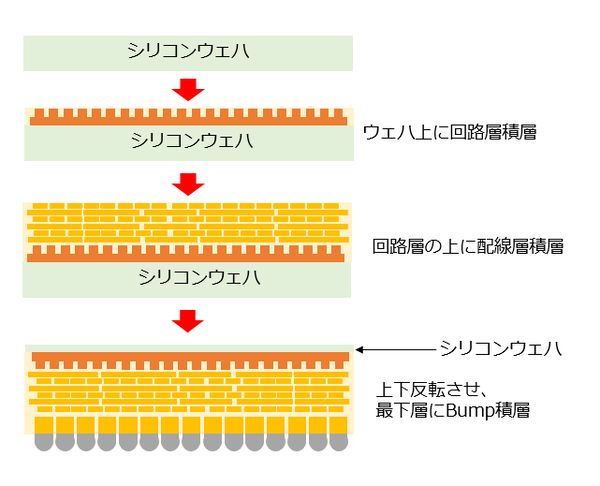

さて次がFoveros Omniであるが、これは「2つのチップ」を高効率に積層するための技術である。簡単におさらいすると、下図が昨今のチップの作り方である。

Flip-Chipと呼ばれることもあるが、要するにダイのすぐ裏にトランジスタの回路層があり、その下に配線層がある形だ。この結果として、2つのチップをそのまま貼り合わせることはできない。

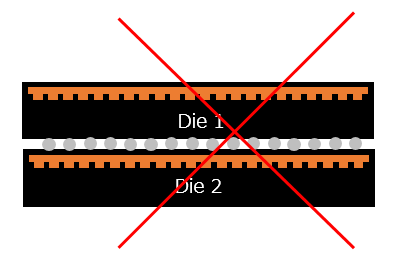

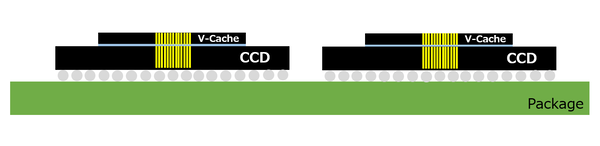

どうしてもやりたければ、回路層の裏のシリコンを貫通するようにTSVを構築して、配線層を裏側まで引っ張らないといけないのだが、当然これはコストがかかるし、そのTSVがある部分には回路を入れられないためダイサイズ的にも効率がよろしくない。AMDの3D V-Cacheの模式図で、中央にTSVを集中的に配しているのは、ダイ全体にTSVを設けるのは面積的に不利だから、という非常に現実的な理由である。

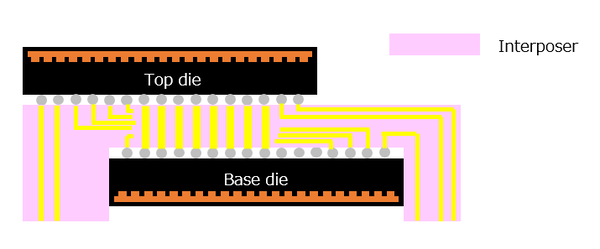

ただ、2チップに限って言えば、下図のような方法が取れる。配線層同士が向かい合うように、Base dieを上下反転させれば、配線長を最短にできることになる。

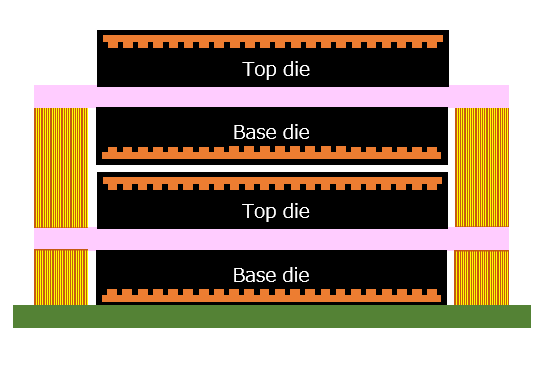

Foveros Omniは、要するに下図のような構成になっていると思われる。

Foveros Omni。Base dieとTop dieで直結できるところはTSVを使って最短距離で接続され、それ以外(おそらく電源など)は、インターポーザー経由でパッケージ裏面に接続されているように見える

もちろんこれだけでは3チップ以上の積層は不可能だが、そうしたニーズは従来のFoverosと同じくチップの外側にViaを設け、これでインターポーザー同士を接続するようにすればよい。つまり2ダイづつ重ねる方法だ。

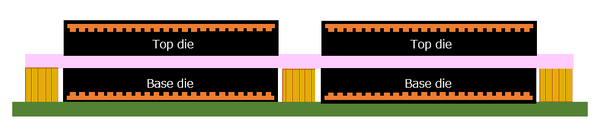

もう1つ、複数のチップを並行に並べながら向かい合わせにする方法も考えられる。発熱が多いチップの場合、あまり縦積みにすると放熱が非常に厳しいことになる。そうした場合、下図のように水平方向に展開する方が効果的かもしれない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ