3D積層技術Foverosの構造はInFOに酷似

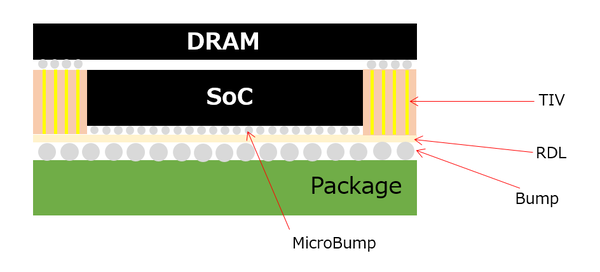

次がFoverosだ。現時点もでインテルはFoverosの詳細を公開していないため、正確なところは藪の中のままであるのだが、基本的にはTSMCのInFOにかなり近いものと思われる。InFOの構造は連載618回で紹介したが、要するに積層するチップの底面にインターポーザー(TSMCはRDL:Re-Distribution Layerと称している)を挟み、このインターポーザー同士をViaで接続するという仕組みである。

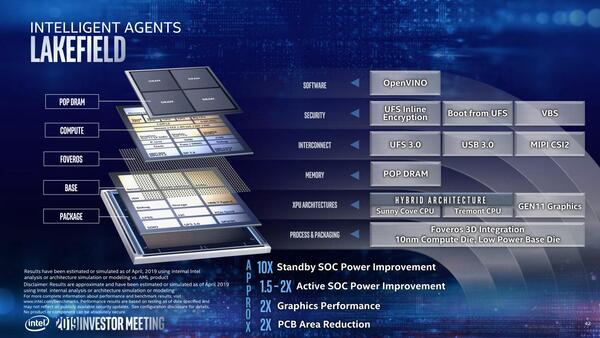

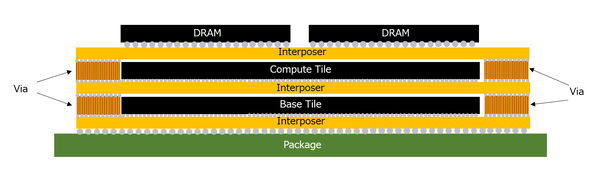

この仕組みなら、3層以上の積層もそう難しくない。実際Lakefieldの場合、DRAM、Compute Tile、Base Tile(PCH)という3層構造になっている。

この説明の図版ではあたかもCompute TileとBase Tileが直接つながっているように見えるが、実際には下図のような構成だとすれば無理なく積層可能なのは納得である。

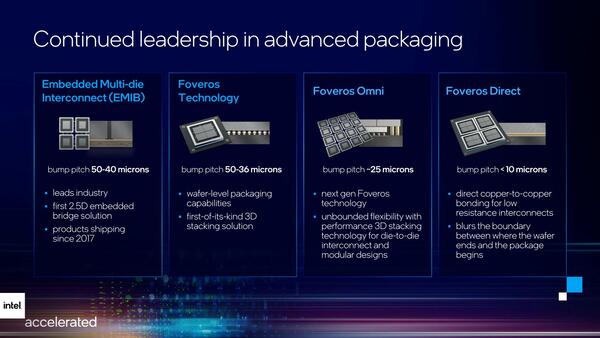

さてこのFoverosは現時点ではまだ第1世代であるが、間もなく第2世代のFoverosが投入されるとともに、新たにFoveros Omni/Foveros Directと呼ばれる技術が発表された。

まず第2世代Foverosだが、Bump Pitchを36μmまで縮めるとともに最大125Wまでの熱環境に対応できる、とされた。

わからないのが、なぜMeteor LakeがFoverosを使うのか? ということ。まさかGPU Dieは1つあたり96EUで、2つ重ねると192EUとかなのだろうか? Compute Dieの方も、1枚では例えば4L+4S構成で、これを2枚重ねると8L+8S構成になるのかもしれない

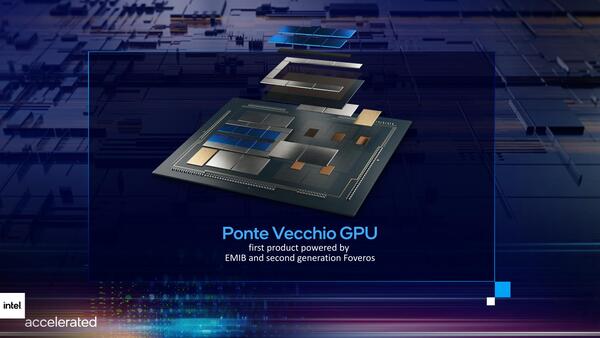

ちなみにEMIBとの併用も可能で、それもあってPonte VecchioはHBM2eはEMIB経由だが、それ以外のコンポーネントは第2世代Foverosを利用して構築される、としている。

Ponte Vecchioは合計47タイルから構成される。内訳はRaja Koduri氏が説明している

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 - この連載の一覧へ