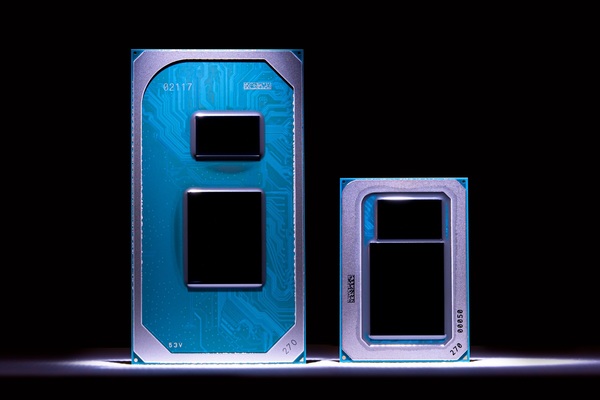

CPUとPCHの統合でダイサイズが肥大化

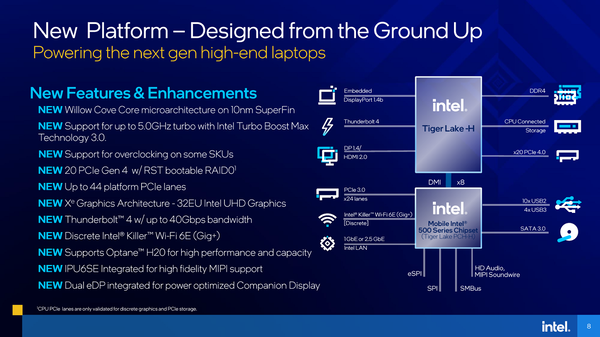

KTU氏による発表記事のスライドにもあるように、少なくとも論理的にはCPU本体とTiger Lake PCH-HというPCHが別々に存在し、間がDMI 3.0×8で接続される構造になっているが、物理的には(Ryzen Gなどと同じように)ワンチップ化したことになる。

ワンチップ化そのものは別に珍しい話ではなく、これまでも例えばGoldmontベースのApollo Lakeなどは1つのダイにCPUとPCHを統合していたので、これが初めてというわけではない。強いて言うなら、PCHに10nmプロセス(それも10nm SuperFin)を使ったのはこれが初めてというあたりだろうか。

PCHのエリアに関してはわりと適当である。3つ前の画像では、ダイ左上に全体の8%程度の面積として入れてあるが、もう少し小さいかもしれない。というのは、上の画像の図にもあるように、Tiger Lake PCH-Hの機能は限られているからだ。

まずIntel Killer Wi-Fi 6Eはディスクリートなので、実際はPCIeの先に拡張カードの形で接続される。またSATA 3.0は一応あるにはあるが、ポート数自体は1か多くても2ポートだろう。

ノート向けであればそもそもSATAポートが多数用意される必要がない。もう最近はDVD-ROMドライブを搭載する機種も激減したし、せいぜいがデータ用にSATA SSDを拡張できるポートがあれば十分というあたり。性能が必要な場合はNVMe SSDを使えばいいからだ。

仮になにか特殊な理由でOEMがどうしても多数のSATAポートが必要というなら、ポートマルチプライヤーを使ってSATAポートを増やすこともできるから、これはOEM側だけで対応できる。となると、PCIeレーンとUSB、1/2.5GbE、HD Audio、SMBus、SPI/eSPIあたりがあればいい。

USB 3までであればすでに実績のあるコントローラーが多数あるし、エリアサイズも小さい。PCIeはさらに簡単で、Root Complex(PCIe全体を制御する部分)はホスト(つまりTiger Lake-Hのアンコア部)に搭載されているから、PCHの側は単にPCIeスイッチが入っているだけである。

その他のI/Fもあまりエリアサイズを喰いそうなものはないので、上で8%ほどのエリアサイズと推定はしたものの、実際には5~6%で収まっている可能性もある。

余談になるが、通常PCHは結構なエリアサイズを喰う。理由はアナログ回路に必要な受動部品(特にコイルとコンデンサー)は微細化と無縁(どうしてもそれなりのサイズが必要)なためだ。ただTiger Lake PCH-Hではこうしたアナログ回路がほとんど搭載されていないようで、そのあたりも統合できた理由かもしれない。

もっともこれは言い方を変えれば、インテルはアナログ部品まわりは鬼門で、これまでもいろいろな不具合を出しまくっているだけに、極力PCHにアナログ回路を含まない方向にシフトしているようで、そうしたことも結果的にPCH統合に貢献しているのはなんというべきか。

これはインテルだけでなくAMDや昨今のARM SoCも同じで、プロセッサー性能を引き上げる&製造コストを引き下げるためにはなるべくチップセットの類を1つのダイに統合する必要があるが、その一方で先端ロジックプロセスは、あまりアナログ統合が得意ではない。

であれば、アナログ部品がどうしても必要なら別チップに切り出す方向で、なるべくデジタル回路(とデジタルI/F)だけでチップセットを完結させる方向にシフトしつつある。その意味でもインテルの方向性は間違ってはいないのだが。

話を戻すと、このPCHを統合したことも、ダイサイズの肥大化に一役買っているのは疑う余地もない。それでもCPU+PCHで2ダイになったTiger Lakeとどちらがコスト的に有利か、は微妙なところである。

訂正:記事公開後にインテルが仕様を公開し、Tiger Lake-HのPCHは統合されておらず、別チップであると判明しました。詳細は連載617回で説明しておりますので、そちらをご参照ください。(2021年5月31日)

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 - この連載の一覧へ