Ice Lake-SPのダイサイズは巨大

ウェハー1枚から77個しか取れない

3月18日に、新CEOであるPat Gelsinger氏が「3月23日に最新情報をウェブキャストで流す」とメンションしたが、その予告ページに掲載された写真が、どうみてもIce Lake-SPの28コア版である。

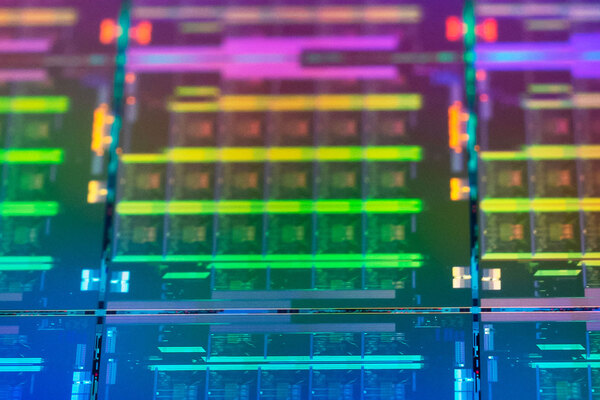

実際、中央を切り出した写真とIce Lake-SPの模式図を比較するとそっくりである。

上の画像の中央を切り出した写真。手前左端がPCIe Gen4で、そこから右に向かって順にメモリーコントローラー、Ice Lakeコア、メモリーコントローラー、Ice Lakeコア×2、PCIe Gen4とくる。模式図の右端の並びである

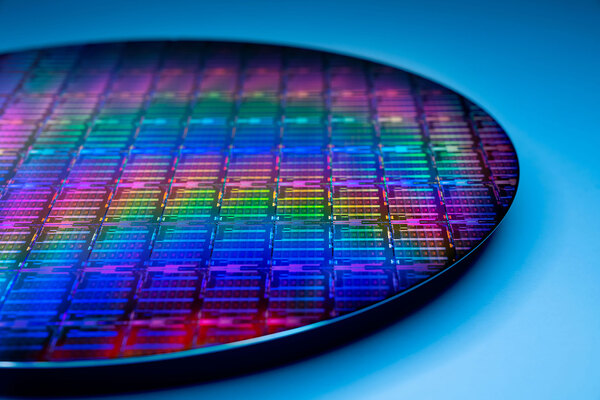

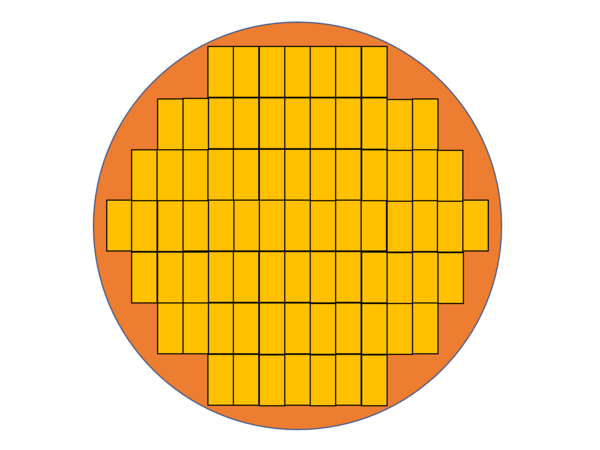

これがIce Lake-SPのウェハー写真だ、という前提で再び予告ページに掲載された写真を見直すと、ウェハー上の配置はおおむね下図のようになる。推定ダイサイズは37×18mm前後で660mm2近くなる。ウェハー1枚から、わずか77個しか取れない計算だ。相変わらず巨大なダイの形で提供されることになりそうである。

Xe-HPGが発表?

最後はGPUの話だ。3月19日、Intel Graphicsの公式アカウントが謎のティザーを公開した。

Xe HPG microarchitecture teaser = ???? pic.twitter.com/kdzBokBiW4

— Intel Graphics (@IntelGraphics) March 18, 2021

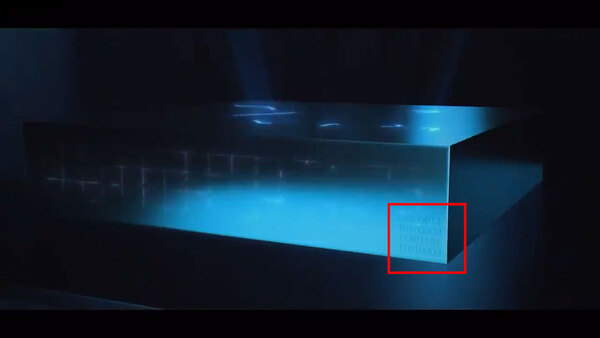

Xe-LPと書かれたチップ(?)に光があたり、Xe-HPGに変化してゆくというものだが、変化し終わったチップ(?)の側面に謎の数字が記載されている。

どう見ても二進数なので、これを十進数にすると35、160、237、208になる。そこでhttp://35.160.237.208/ に行くと、https://xehpg.intel.comにリダイレクトされる。

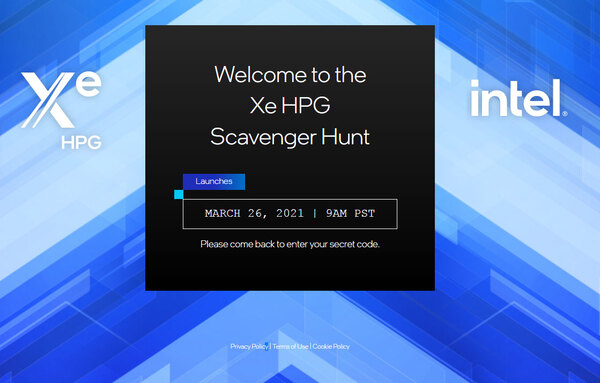

https://xehpg.intel.comのページ。Scavenger(ゴミあさり)呼ばわりされるし……(scavenger huntは借り物競争という意味なので、インテルに悪意がないのは理解しているが)

おそらくは3月26日の朝9時(太平洋時間:日本時間で3月27日の深夜2時)に「何か」が発表されるようだ。Xe-HPGの製品発表というのが一番普通の予測であるが。これに関しては今のところ事前情報がなにもないので、筆者もとりあえずは楽しみにしていたいと思う。それはともかく、Twitterのブロック解除してもらえませんかね……

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ