今回はインテルのCPUロードマップアップデートだ。Rocket LakeとIce Lake-SP、最後にXe-HPGの話をしよう。CPUロードマップと言いつつ、最後にGPUの話も入っているが、まぁいいだろう。

Rocket Lakeアップデート

Cypress CoveはSunny Coveの14nm版

米国時間の3月16日にRocket Lakeの詳細が公開され、ジサトライッペイ氏によるレポートも上がっているが、このレポートにいくつか補足を入れたい。

まずCypress Coveの話を。ジサトライッペイ氏によるレポートではWillow Coveの移植とあるが、実際にはSunny Coveの移植(というよりバックポート)である。

要するにTiger Lakeを14nmに持ち込んだのではなく、Ice Lakeの14nm版である。時系列的に言っても、Tiger Lakeの出荷開始は2020年9月なので、シリコンの検証が終わったのは早くても2020年5月か6月。ということはテープアウトは2019年末~2020年初頭と思われる。

ここから14nm++にバックポートしたら、テープアウトは2021年末になりかねないので、どう考えても間に合わない。Ice Lakeはすでにモバイル向けに加えてXeon向けのSkylake-SPの実装もとっくに終わっているし、そもそもインテルのツイートにもあるように、Ice Lakeの最初のテープアウトは2017年6月のことである。

Another milestone for 10nm: Cannon Lake on track and we’ve now taped in Ice Lake, our 2nd-generation 10nm product. pic.twitter.com/DUDm3MsBaB

— Intel News (@intelnews) June 8, 2017

この時はまだ14nmにバックポートする予定はなかったはずだが、その意味ではこの後はいつでもバックポートを始められたわけだ。昨年7月に7nmプロセスの遅延が発表されたが、社内的にはこれより前に「駄目そうだ」という観測は当然あったわけで、どこかのタイミングでバックアッププランとして10nm向けアーキテクチャーのバックポートを始めたとしても不思議ではない。そうなると当時利用できるコアはIce Lakeしかなかっただろうし、Ice Lakeを利用するのが妥当であっただろう。

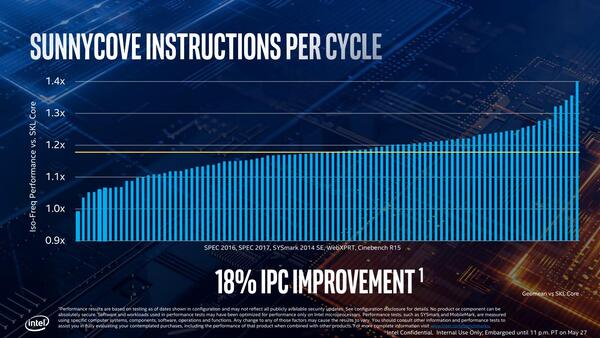

そのRocket LakeはComet Lake比で19%の性能改善があるという話になっているが、もともとIce LakeはSkylake比で18%のIPC向上があるという話であり、Tiger LakeはIce Lakeに対してさらにキャッシュ周りの改良を加えているから、おそらくIPCの向上率は20%を超えるだろう。

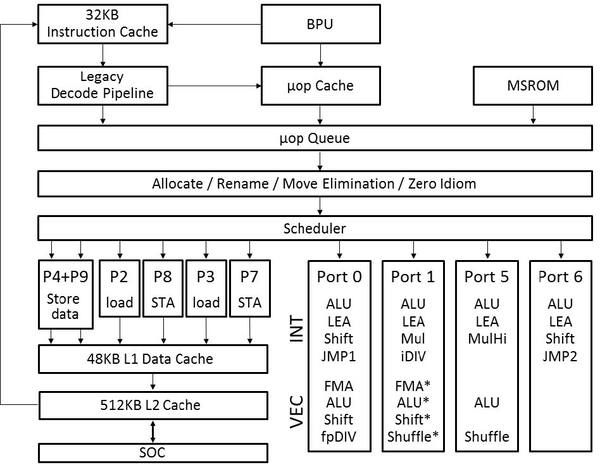

Ice LakeはSkylake比で18%のIPC向上がある。画像は連載514回より

ちなみに、1%の差はどこから出てきたかは不明だが、メモリーコントローラーの差(DDR4-2933→DDR4-3200あたり)かもしれない。

プロセスそのものは基本的にはComet Lakeと同じ14nm++であるが、「随時プロセスの改良を進めているので、細かな最適化などはしているから厳密に言えば若干異なる」という話であった。Sunny Coveベースということは、当然キャッシュ構成などもIce Lakeと同じになる。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 - この連載の一覧へ