ロードマップでわかる!当世プロセッサー事情 第581回

謎が多いGeForce RTX 3000シリーズのプロセスとGDDR6X NVIDIA GPUロードマップ

2020年09月21日 12時00分更新

8LPPを採用した要因は生産量とコスト

ではなぜ7LPPを使わずに、8LPP派生型の8Nを使ったか? 可能性としては以下の3つが考えられる。

- Defect(欠陥)が多くて使えなかった

- 生産量的に間に合わなかった

- コストが高くなりすぎた

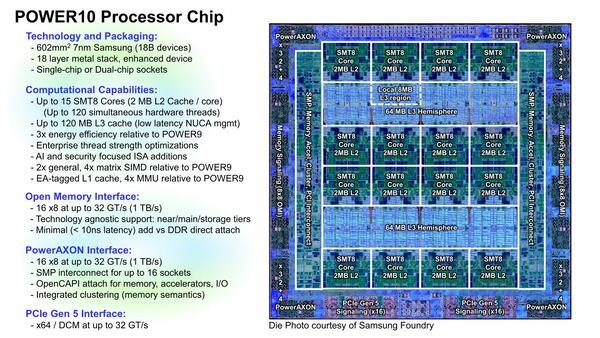

ただ、1番目に関してはそれほどシビアではなかったと思われる。というのは、IBMはそのSamsungの7nmを使ってPOWER10を製造することを今年のHotChipsで発表しており、少なくとも600mm2のダイまではある程度の歩留まりで製造できることが見えている。

したがって、400mm2台のダイの製造の歩留まりはおそらく問題にならない程度に収まったと思われる。それだけA100の800mm2オーバーが論外という話ではあるのだが。

2番目は割と真実味のある話である。まだEUVを利用した場合、スループットはそれほど上がらない。正確な数字ではないが、おおむねArF+液浸を使った場合、1台のステッパー(露光機)で1日6000ウェハー程度を処理できる。

ところがEUVでは、これが2018年当時でおおむね1日1500ウェハー程度。現在はもう少し上がってるらしいが、それでも2000ウェハー/日まで向上しているかどうか、というあたりだろう。仮に2000ウェハーだとして、生産量が1/3に落ちる計算だ。

もちろんこれはマルチパターニングなら話が変わってくる。ダブルパターニングだとArF+液浸で3000ウェハー/日、トリプルパターニングで2000ウェハー/日なので、そうなるとすでにEUVステッパーの性能は、ArF+液浸のステッパーと性能が変わらないというのがEUV推進派の主張である。

この主張そのものは正しいのだが、問題はEUVステッパーは極端に高価(1台1億2000万ドル!)なことで、ArF+液浸のステッパーはその半額未満である。

通常ファウンダリーはステッパーが1台ということはなく、複数台が並行して動いているわけだが、EUVのステッパーはそこまでの台数をそろえるのが難しい。なので1台あたりのスループットが同じであっても、台数の差でEUVステッパーを利用したウェハーの生産量は限られる。

これはPOWER10やそれこそA100のような「ダイサイズは滅茶苦茶大きいが、必要とされる数はそれほど多くない製品」、あるいはダイサイズが100mm2を切るモバイル向けSoCのように「1枚のウェハーから大量に取れるので、結果的にウェハー数を抑えられる」製品には使えるかもしれないが、GA102のような「ダイサイズが大きく、しかも出荷数量も多い」製品にはなかなか厳しいことになる。

3つ目はコストの話である。現状EUVを利用したプロセスは、ArF+液浸とコストがそれほど変わらない。理由はEUVのステッパーの償却費が乗っかるためだ。

ArF+液浸の場合、複数回ステッパーを廻す(*1)のと、その複数回の露光にそれぞれ異なるマスクが必要なため、これの初期コストがバカにならないのがコスト高騰の主要因である。

(*1) 正確に言えばステッパーで露光してから、それをCMP(化学機械研磨)などで削って、必要なら別の材料を補填して、またステッパーをかけて、という具合に処理プロセスが急激に増える。

EUVはこれが1回の露光で済むから経済的というのは事実そうで、マスクコストは大幅に減るのだが、その分1回の露光に必要なコストが急激に上がっている。

ちなみにEUVのステッパーを稼働するのには1MWの電力が必要とされる。この電気代もシャレにならない。こうなってくると、EUVを使って400mm2のダイと、ArF+液浸で600mm2のダイのどちらが安いかという、わりと真剣な議論になる。

おそらく今回の8LPPを使うという決断は、生産量とコストの両面が主要因だったと思われる。というより、NVIDIAのBig Die志向が続く限り、この決断はやむを得なかっただろう。その代償が、Board Power 320Wや350Wというバカみたいな消費電力である。

540億トランジスタのA100が400Wなのに、280億個とほぼ半分のGA100がこんなに消費電力が多いのは、動作周波数の差もあるとはいえ、明らかに8Nプロセスを利用したためである。

そもそも10LPE→10LPP→8LPPという一連の改良の中に省電力化の改良が一切入ってないあたり、これはやむを得ない選択だったのだろう。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ