5LPEでは7LPPと比べて

面積を0.7倍に、消費電力を0.8倍にできる

さて、ここまでは現状の話であり、ここからは今後の話である。前回、7nmプロセスを使った製品について、Ampereというコード名の製品が用意されているという話をしたが、これは前回も推察した通り、Voltaの後継となる模様だ。要するにTeslaシリーズのHPC向けである。

そして、これとは別にもう1品種、7nmでの開発が進んでいる。ただしこちらもデスクトップ向けではない。

やや話が飛ぶが、今年10月にサンノゼで開催されたArm TechCon 2019の中に、ARMと半導体ベンダーのCadence、それとSamsung Foundryの3社による共同テクニカルセッションがあった。

このテクニカルセッションのテーマは5nm世代のARMコアであって、ARMの次世代コア(Hercules)をSamsungの次のメジャーノードである5LPEに対応させるための環境やタイムラインについて紹介したものである。

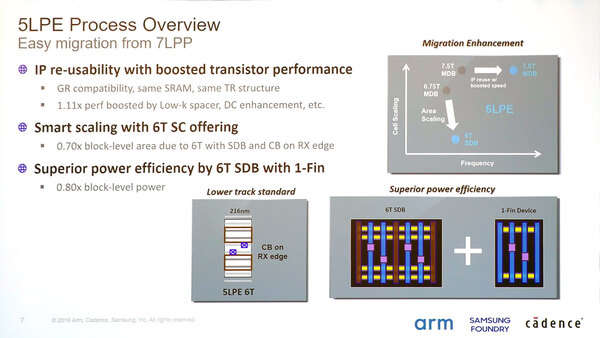

それはともかくとして、この5LPEの特長などがSamsung Foundriesによって語られているのだが、5LPEは基本的に7LPP、つまりEUV(極端紫外線)を利用する第一世代の設計をそのまま踏襲しながら、性能を最大で1.1倍に、面積を0.7倍に、そして消費電力を0.8倍にできるとしている。

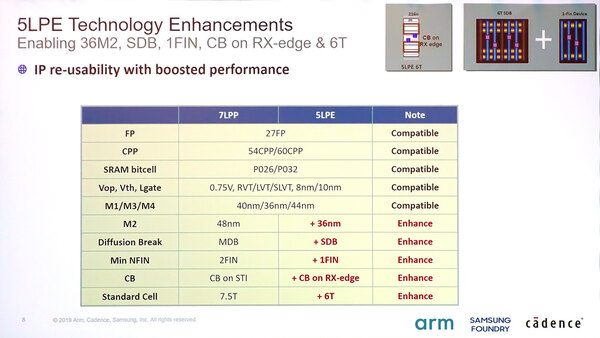

具体的に、7LPPと5LPEの2つのプロセスのパラメーターをもう少し詳細に説明したのがこちらである。

7LPP→5LPEでは、7LPPがMixed Diffusion Break、5LPEがSingle Diffusion Breakとなっている。Diffusion Breakとはなにかというと、インテルではDummy Gateと呼んでいるものである。

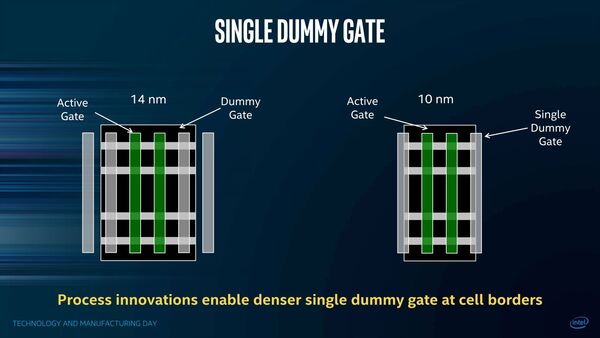

連載419回の中で解説した画像がわかりやすいが、1つのセルの両端にDummy Gateを設けるのがDouble Dummy Gate、あるいはDouble Diffusion Breakと呼ばれる方式、2つのセルの間で1つのDummy Gateを共有するのがSingle Dummy GateあるいはSingle Diffusion Breakと呼ぶ。

ではMixed Diffusion Breakは? というと、PMOSはSingle Diffusion Break、NMOSはDouble Diffusion Breakを利用するという折衷タイプの構成であり、これを利用してNMOS側にストレスをかけることで性能を上げる(歪トランジスタ的な効果をおよぼす模様)ものだが、Dummy Gateが1つ余分に必要な分、若干エリアサイズは増える。これをSingleにすることでエリアサイズの削減が可能になる、という仕組みである。

ただ一番大きいのは一番下にあるStandard Cellの構成で、7LPPが7.5トラック構成なのが、5LPEでは6トラックに減る。これにより、Standard Cellの面積は20%ほど削減される形だ。

連載419回で解説したDummy Gateの画像では30%の面積削減としているが、このうち20%はこのStandard Cellの縮小で実現されていると見られる。

ただ、この20%削減がそのまま「ダイサイズも20%削減になる」とならないのは、Standard Cellを縮小すると、当然1つのStandard Cellで収まらないロジックが増えるからだ。つまりトータルで面積が減るかどうかは設計次第となる。

一般論的に言えば、比較的簡単なロジックについてはトラック数に比例して面積が減る一方、複雑なロジックではセル数が増えるものの、セル自身の面積が小さくなっているので、トータルではやや面積縮小となることは多いが、20%減るケースはまれだろう。

先の画像のキャプションで「Block level」の定義に起因すると書いたのはこれが要因である。今のところSamsungの言う「Block level」の定義がよくわからないが、これは理論値であって実際にはここまで面積は減らないと考えたほうがいい。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 - この連載の一覧へ