X570チップセットに

第2世代Ryzenを載せたときの挙動

次にチップセット周りについて。連載513回の最後で、X570に第2世代Ryzenを装着した場合にどういう振る舞いになるのか、という点が不明だとしたのだが、これについて確認が取れた。

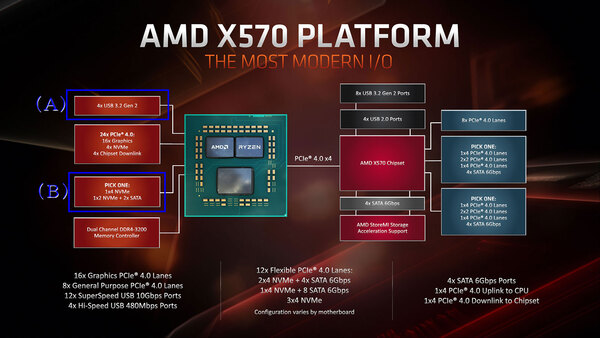

まず上の画像の(A)にあたるUSB 3.2 Gen2×4であるが、これは第2世代Ryzenを搭載した場合、USB 3.1 Gen1相当(USB 3.2 Gen1といっても良いが、要するにUSB 5Gbps相当)にダウンするとのこと。

次いで(B)の、1×4 NVMeに関しては第2世代Ryzenでは無効になるという話であった。おそらくではあるが、第2世代RyzenのCPUピンにはそもそもこの1×4 NVMe向けのPCIeの信号が出ていないのではないかと思われる。

またGPU接続用のx16のPCIeレーンも、X570との接続用のx4 PCIeレーンも当然Gen3相当になり、この場合X570から出るPCIeもすべてGen3相当になるという話だった。

ただこの場合でも、チップセットから出る8ポートのUSB 3.2 Gen2ポートはそのままUSB 3.2 Gen2として有効とのことであった。これは妥当な構成なのではないかと思われる。

メモリーはDDR4-5133まで可能

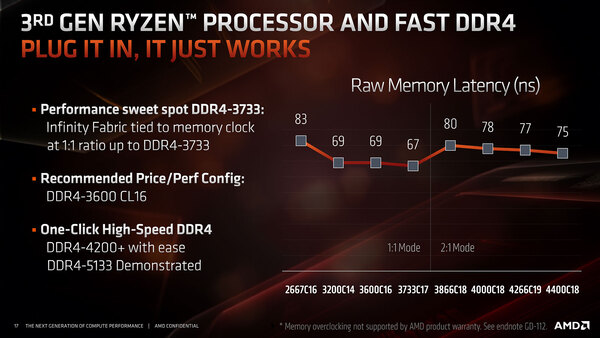

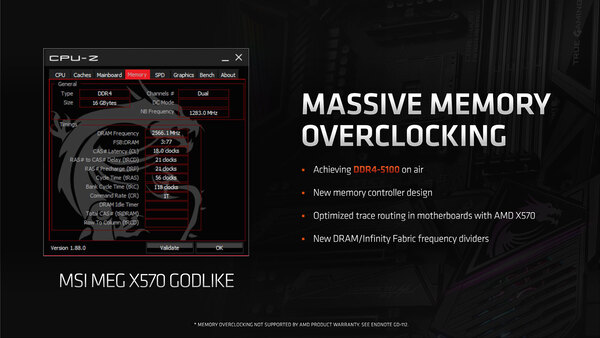

チップセットの話が出たところでついでにメモリーコントローラーの話もしておこう。第3世代Ryzenは、定格がDDR4-3200まで、という話は連載513回でレポートしたが、実際はというとDDR4-4200あたりまでは軽く行けて、DDR4-5133までは可能という説明があった。

ここに出てくる1:1Modeと2:1Modeであるが、これはメモリークロックとインフィニティーファブリックのクロック比である。

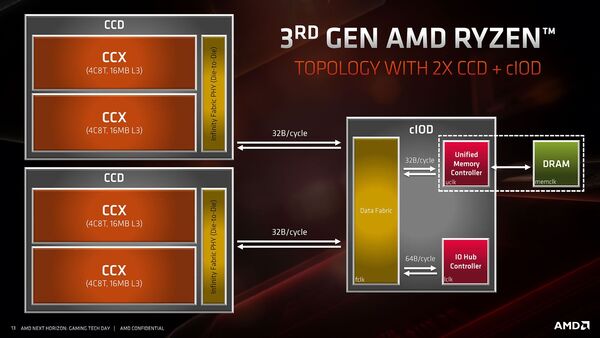

前回の記事の図で、I/Oチップレット(cIOD)側を見ると、メモリーのクロック(memclk)とメモリーコントローラーのクロック(uclk)、それとデータファブリックのクロック(fclk)が別々のクロックソースになっていることが示されている。

1:1 Modeの場合、memclkとuclkが連動し、ということはuclkとfclkも連動するために、あまりmemclkを上げすぎるとインフィニティーファブリックのスピードが上がりすぎて動作しなくなる。

そこでDDR4-3866(つまりmemclkが1933MHz)以上の場合、uclkとfclkの比を2:1にすることで、インフィニティーファブリックの速度が上がりすぎないようにできるという話である。これを利用すれば、DDR4-5133も夢ではないというわけだ。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ