Atomの新アーキテクチャー

Tremont

チップセットの話はこのあたりにして、ここからはCPUアップデートの話だ。前回はCoreアーキテクチャーのみを紹介したが、Atomにも若干のアップデートがある。

インテルのRonak Singhal氏(Intel Fellow, Core and Visual Computing Group Director, CPU Computing Architecture, Intel Architecture Cores Group)が4月5日にこんなTweetをしている。

Latest version of our document with upcoming ISA extensions now available, including some new instructions detailed for the first time: https://t.co/bV2QC2Uw8M

— Ronak Singhal (@rsinghal1) 2018年4月4日

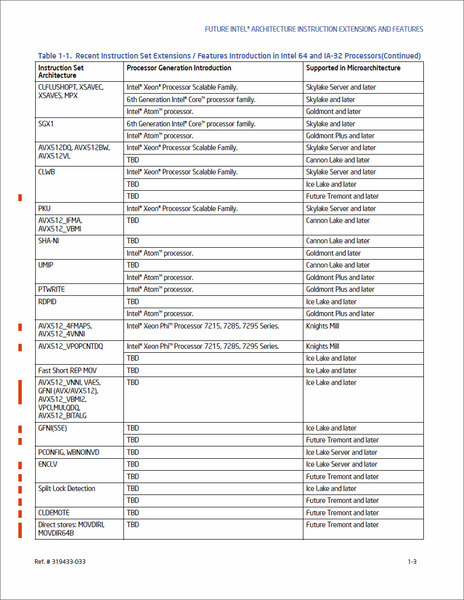

アップデートされたのは“Intel Architecture Instruction Set Extensions and Future Features Programming Reference”で、名前の通りx86/Intel 64の命令セット一覧である。ここのFeatureページにTremontの文字が出現したことで、ちょっとした騒ぎになった。

このマニュアルはあくまで命令セットであって、マイクロアーキテクチャーがどうなってるという話は一切載っていないため、Tremontがどんなものなのかはさっぱりわからない。

マイクロアーキテクチャーが載っているのはIntel Softwareの“Intel 64 and IA-32 architectures optimization reference manual”の方だが、見ていただくとわかるがGoldmont Plusどまりである。

このTremontは、コード名一覧にも載っていない。今回追加されている命令はAVX系ではなくIntel 64の方で、以下のようになっている。

| 追加された命令 | ||||||

|---|---|---|---|---|---|---|

| 命令 | 搭載マイクロアーキテクチャー | |||||

| GFNI(SSE) | Ice Lake and later Future Tremont and later |

|||||

| ENCLV | Ice Lake Server and later Tremont and later |

|||||

| Split Lock Detection | Ice Lake and later Tremont and later |

|||||

| CLDEMOTE | Tremont and later | |||||

| Direct stores: MOVDIRI, MOVDIR64B | Future Tremont and later | |||||

| User wait: TPAUSE,UMONITOR, UMWAIT | Future Tremont and later | |||||

登場時期はIce LakeやIce Lake Server(Ice Lake-SPのことだろう)より後になると思われる。ということは、製造プロセスは10nmと考えるのが妥当だろう。

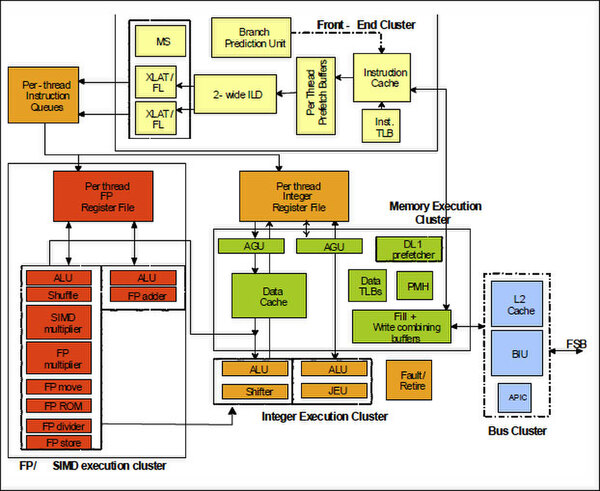

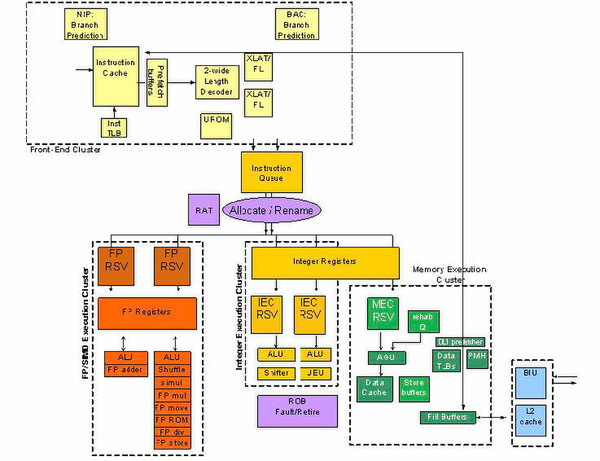

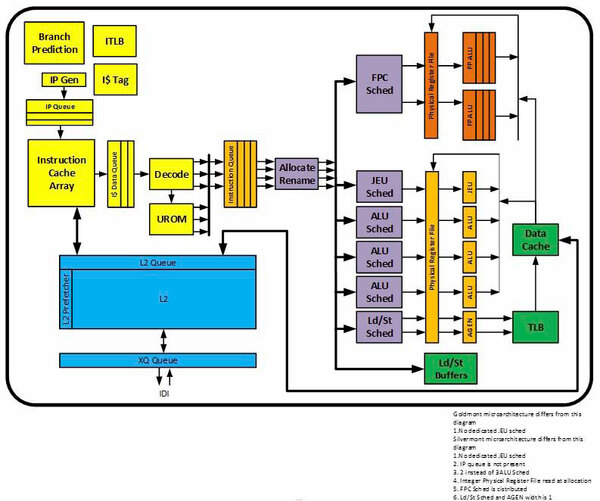

ちなみにAtomの場合、当初のBonnell(45nm)/Saltmont(32nm)はIn-orderの2命令同時実行(Photo02)、Silvermont(22nm)/Airmont(14nm)は2命令発行のOut-of-Order(Photo03)、Goldmont(Photo04)/Goldmont+(Photo05)は3命令同時発行のOut-of-order構成である。

ということは次は4命令同時発行か……という考えがよぎるが、そこまで行くとCoreとの差がなくなり、同程度に巨大なダイになりかねない。消えてしまったKnights Hillに搭載予定だったAtomコアにはひょっとして、という話があった。

というのはその前世代のKnighs LandingはAtomコアに2つのVPU(AVX-512ユニット)を組み合わせたものだが、仮にKnights Hillでも同じ構成だとすると、2つのVPUをフルに活用するためにはロードストアユニットも2つ(VPUあたり1つ)ないと帳尻が合わなくなるからだ。

VPU2つとロードストアユニット2つを同時に動かすためには4命令同時発行でないと間に合わないわけで、ここから4命令という話が出てきた。

ただKnights Hillが消えた今となっては、そこまでのピーク性能は求められないため、個人的には3命令のままなのではないか、と考えている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 - この連載の一覧へ