前回はQCDOCの説明をしたので、今回はQCDOCを元に作られたBlue Gene系列の話である。

Blue Gene/L

前回も少し触れたが、元々IBMは1999年にProtein Folding(タンパク質の構造解析)を目的とした1億ドル規模の研究開発プロジェクトを立ち上げる。

このプロジェクトは、Protein Foldingのメカニズムを大規模シミュレーションで解明するのが目的であるが、これとともにMassively Parallel(超並列)のハードウェアとソフトウェアを構築することも目的であった。

Protein Foldingのシミュレーションのためには1PFLIOS規模のマシンが必要ということで、プロジェクトの最終目標は1PFLOPSのマシンを構築することにあった。

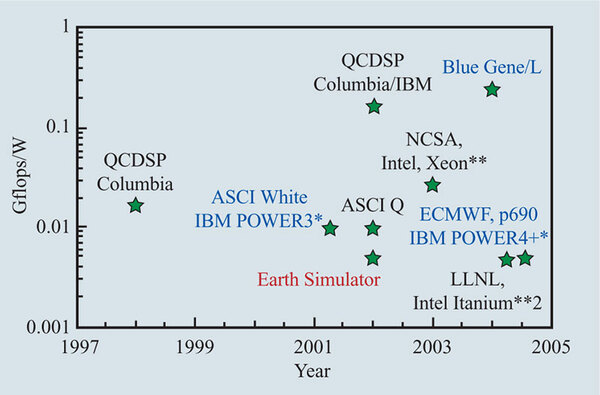

1999年といえばASCI Blue Pacific/Blue Mountainが運用を始めた年であり、ASCI Blue Mountainが実効1.6TFLOPS、Blue Pacificでも実効2.1TFLOPSというあたりで、1PFLOPSといえばこの500~600倍の性能になるため、これを一足飛びに実現するのは到底無理である。そこで当初は300TFLOPS規模のマシン(Blue Gene/L)を実現することを目標とした。

低コストで高性能を求められた

Blue Gene/L

さて、その最初のBlue Gene/Lである。設計目標は高い性能/コスト比を実現することにあり、さらに性能/消費電力比や性能/体積比を向上することも目標に掲げられた。最初の2つは理解しやすいとして、最後の性能/体積比は、あまりなじみがないだろう。

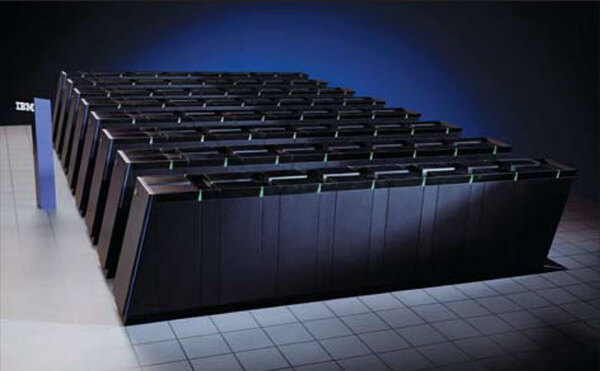

これは、ASCIシステムがいずれも10000平方フィートを超えるような膨大な設置面積を要していることへの反省である。前回紹介したQCDOCが100平方フィート程度で収まっていることはシステムの運用コストという点でもメリットは大きい。

そしてもう1つ、設置面積が大きいとノード間を引き回す配線の距離も長くなるという意味で、これはそのままレイテンシーや消費電力の増大につながる。したがって、可能ならばなるべく配線距離は短くしたいし、すると必然的に設置面積を抑える方策が必要になる。

Blue Gene/Lはこうしたことを勘案し、既存のスーパーコンピューターを大きく上回る性能/消費電力比を目指すことを目標に掲げた。

その実現のために、QCDSP/QCDOCの考え方を発展させることとなった。性能目標は360TFLOPSで、これを20MW程度の消費電力でまかなうというものだ。

PowerPC 440コアと

小容量キャッシュを採用

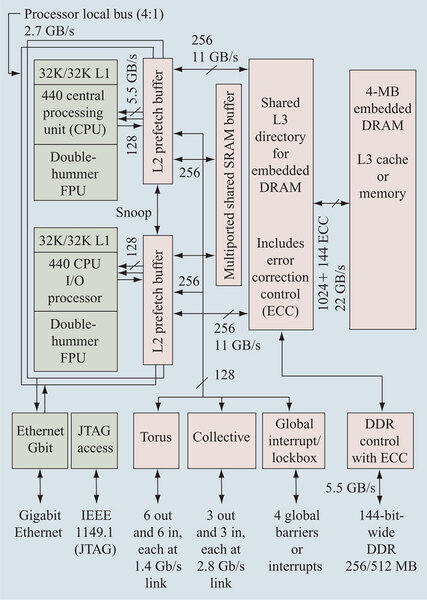

この目標をどう実現するかであるが、基本はQCDOCと同じくPowerPC 440コアを利用している。これに独自のDouble-hummer FPUを組み合わせたものが1コアである。

チップそのものはこのコアを2つに、2次キャッシュ×2、さらにeDRAMを使った4MBの3次キャッシュ、そのうえ外部接続用のネットワークとDRAMコントローラーなどを統合している。

これにより、DRAMを除くと事実上1チップで2つの計算ノードを統合できる。製造プロセスは8SF(130nm)が用いられているが、動作周波数は700MHzと控えめになっている。これはCPUコアの消費電力のターゲットが1Wとされ、これにあわせて調整した形だ。

2次キャッシュの構造もおもしろい。上の画像でL2 prefetch bufferと書かれているのは、容量が2KBしかないためで、32KBの1次キャッシュと比べてもだいぶ少ない。なので当然ながらInclusive構造には出来ず、Exclusive構造としている。

なぜこんな小容量のキャッシュを追加したかと言えば、Cache Snoopingのためである。PowerPC 440そのものはシングルコアのCPUなので、マルチプロセッサーの対応が入っていない。

具体的にはCache Snoopの機能を持っていないので、このままだと外部に共有キャッシュを一切持てなくなる。これをカバーするために、Cache Snoopの機能を2次キャッシュに持たせた形だ。

あくまでSnoopingを目的としているから容量は少なくても良く、このためもあってかL2 CacheではなくL2 Prefetch Bufferと称している。

容量そのものはembedded DRAMを利用して4MBもの大容量をL3オンチップで搭載しており、しかもこれが十分に高速となっている。

Double-hummer FPUは700MHzで2.8GFLOPSの演算性能を持つが、Doubleの場合にはこれをフルに使う場合には以下の処理が発生することになる。

- 元データを5.6GB/秒×2で読み込み

- 演算結果を5.6GB/秒で書き出し

上の画像を見るとわかるとおり、CPUコアと2次/3次キャッシュをつなぐバスは、この帯域に合わせて設計されていることがわかる。要するにこれがボトルネックにならないように設計されているわけだ。もっとも帯域はともかくレイテンシーの方は以下のような数字が出ており、2次/3次キャッシュはそれなりにレイテンシーが大きい。

| キャッシュとレイテンシーの関係 | |

|---|---|

| 1次キャッシュ | 3サイクル |

| 2次キャッシュ | 11サイクル |

| スクラッチパッド | 15サイクル |

| 3次キャッシュ | 28/36/40サイクル |

| DRAM | 86サイクル |

むしろDRAMが異様に高速というべきかもしれないが、これは3次キャッシュを経由した時の数字で、3次キャッシュを経由しないともう少し増えると思われる。

→次のページヘ続く (筐体を斜めに配置する独特な構造と外観)

この連載の記事

-

第769回

PC

HDDのコントローラーとI/Fを一体化して爆発的に普及したIDE 消え去ったI/F史 -

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 - この連載の一覧へ