1ヵ月ぶりのスーパーコンピューターの系譜である。前回はASC Purpleまで説明したが、今回はASCI/ASC系列から外れる製品の話をする。それはIBMのBlue Geneにつながる、QCDOCだ。

QCDOC

IBMが1PFLOPSを目指して作った

超並列マシン「Blue Gene」

IBMはASCI/ASCにASCI Blue PacificやASCI White、ASC Purpleといった系列の製品を投入し続けたが、これらはいずれもPOWERプロセッサーをベースとしたSMP(Symmetric Multiprocessing:対称型マルチプロセッシング)+クラスター構成のマシンである。

ところが、これとは別にIBMではMPP(Massively Parallel Processing:超並列)ベースのシステムも開発を行なっていた。これを両方開発できるあたりがIBMの底力と言うべきだろう。

このMPPを全面的に採用したのが、1999年に開発が発表されたBlue Geneである。これは1億ドル規模を費やし、1PFLOPSのマシンを構築するもので、目的はProtein Folding(たんぱく質の折りたたみ構造)の解析にある(関連リンク)。

これがどんなものかの説明は省くので、興味ある方はWikipediaなどを見ていただくとして、とにかく解析のためには膨大な計算量が必要であり、このために高いコンピューター性能が必要とされた分野である。

流石に1PFLOPSを一発で構成するのは無理であり、当初開発されたBlue Gene/Lはピークで360TFLOPSを狙い、1PFLOPSはその後継のBlue Gene/Pで実現することになった。

Blue Geneの起源は

量子色力学シミュレーション用の「QCDOC」

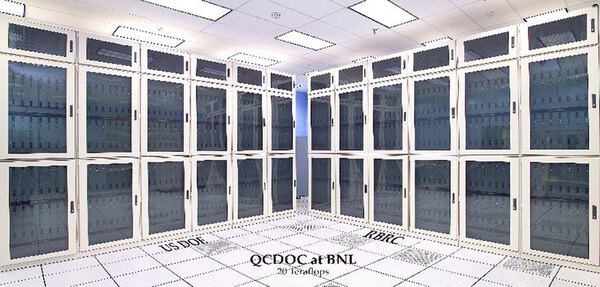

このBlue Geneシリーズだが、元になったのはIBMが英エディンバラ大、米コロンビア大、理研BNL研究センターと共同で開発したQCDOCというマシンである。

この名前はQuantum ChromoDynamics On a Chipの頭文字をとったもので、Quantum ChromoDynamics(量子色力学)のシミュレーションを行なうために設計されたものである。

もっともQuantum ChromoDynamics向けの設計といっても、プロセッサーそのものはごく普通のPowerPCコアである。ではどの辺が独特かというと、運用コストを低く抑えることに留意していた点だ。

核兵器シミュレーションを目的としたASCI/ASCはなにしろ予算が潤沢だったため、システムコストもさることながら運用コストがバカ高くてもそれほど問題はなかった。

例えばASC Purpleの場合、システムそのものの消費電力が7.5MWだった(関連リンク)。やや後の数字になるが、2005年頃の相場では、平均して電気代は0.12ドル/KWh程度とされており、24時間365日稼動させた場合の電気代は788万4000ドルとなる。

つまり年間のシステムの電気代だけで8億円ほど、これに空調のための電気代や設備の照明装置などを加えるとおおむね月あたり1億円くらいになるだろう。

ちなみにこれはあくまで電気代だけの話で、メンテナンス費用を含む全体ではもっと膨大な金額になると予想される。これは到底、大学や民間研究機関単体で維持できるものではない。

また初期費用もASCI/ASCシステムは別格の規模であり、大学などではもう1~2桁落とした金額が求められる。

QCDOCの前身はコスパに優れる

「QCDSP」

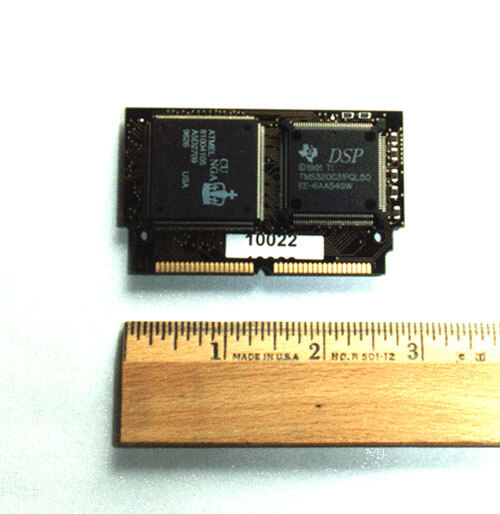

QCDOCの前身が、1993年から開発されていたQCDSPと呼ばれるマシンである。これはTIのTMS320C31という50MHz駆動のDSP(Digital Signal Processor)に、2次元メッシュネットワーク用のカスタムチップ、それと2560KBのDRAMをSO-DIMM上に搭載したものである。

TMS320C31は50MHz駆動で50MFLOPSの浮動小数点演算(ただし32/40bitなので、倍精度ではなく単精度)を行なえるDSPチップ。このTMS320C31を搭載したモジュールを64ノード集積すると約3GFLOPSの演算性能になる。

コロンビア大は最大8192ノードで400GFLOPSのQCDSPマシンを、理研BNL研究センターは12288ノードで600GFLOPSのQCDSPマシンをそれぞれ構築している。

コストパフォーマンスという点では非常に優秀なQCDSPであったし、価格も安かった。コロンビア大の場合、1997年~1998年の2年間で64ノードから8192ノードまで強化したが、トータルのコストは180万ドル程度、うち部品代は120万ドル未満だったようだ。実際、1998年にQCDSPはゴードンベル賞を受賞している。

しかし、DSP単体の性能は1チップあたり50MFLOPSとそれほど高くないうえ、ノード数もそろそろ上限だったため、より高性能な解決案が必要とされた。

→次のページヘ続く (部品点数を抑えて低コスト化を実現)

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ