今年最後の連載は、スーパーコンピューターの系譜の第14回「nCUBE後編」である。1989年、nCUBEは第2世代製品のnCUBE 2を発表する。

先代から大幅に性能が向上した

nCUBE 2

nCUBE 2は初代のnCUBE 10と構成こそ似ているが、以下のようにノードプロセッサーそのものが大幅に性能が底上げされたうえに、最大ノード数も8倍になったことで、より高いシステム性能が望めるようになった。

nCUBE 2の変更点

- プロセスをNMOS 2μmからCMOS bi-metal 1μmに変更。この結果、動作周波数は当初20MHz、後に25/30MHzまで高速化された。ちなみにトランジスタ数は50万個まで増加した。

- ALU(整数演算ユニット)が64bit化。さらに128bytesの命令キャッシュと64bytesのデータキャッシュも搭載する。これら動作周波数向上により、整数演算性能は7MIPS、浮動小数点演算性能は3.5MFLOPS(単精度)に改善した。

- メモリー搭載量も1~64MBに増強。またオンチップでMMUも搭載した。下の画像は1ノード分のボードだが、nCUBE 2プロセッサーと6つの4Mbit DRAMを搭載した2MB構成のものである。

- I/Oリンクは22本から28本(14対)まで増強された。うち1対はI/O用なので、残り13対を利用することで、最大8192node(213)のHyper Cubeを構成可能となった。またリンクの速度は20Mbpsに増強されている。

ちなみにシステムコントローラーは、nCUBE 10のi286ベースPCからSun Microsystemsのワークステーションに変更されている。

このnCUBE 2のシステムもまた、それなりに売れたらしい。もともとnCUBE 10の時には、開発用向けに、4ノード分が搭載されたPCの拡張カードや、16ノード構成のボードも用意されていたが、nCUBE 2では64ノードが搭載された1枚のボードが最小構成という事になった。

ちなみにその最小構成のお値段は、当時の価格でおおむね25万ドルとされている。nCUBEもまた、いくつかの顧客に納入されたが、最大の規模のものはSNL(Sandia National Laboratories:サンディア国立研究所)に納入された1024ノードの構成だった。

このシステムはLINPACKで1.9GFLOPSの性能を出し、1993年6月にはTOP5000に160位でランク入りしている(関連リンク)。

SNLには初代のnCUBE 10のシステムも納入されているが、こちらはTOP500にはランクインしていない。ただ1024ノードのnCUBE 10システムを使って400~600倍の高速化を図ったということで、SNLのRobert Benner/John Gustafson/Gary Montryの3氏が第1回(1987年)のゴードンベル賞を受賞している(関連リンク)。

さて、実はこのあたりからnCUBEの方針が段々変わっていくのだが、その話は後述するとして、先にnCUBE 3の話をしたい。

64bitアドレスをサポートする

nCUBE 3

1995年にnCUBEは後継製品となるnCUBE 3を発表する。nCUBE 3ではついにリンク数が16対となり、フル構成でのノード数は216=65536個が可能となっている。

これだけノード数が多い上に、しかも1ノードあたり最大1GBまでのメモリーが利用可能となっている。ここまでメモリー容量が多い(理論上最大構成では64TB)と、32bitのアドレスでは全然足りないため、nCUBE 3のノードプロセッサーは64bitアドレスをサポートするようになった。

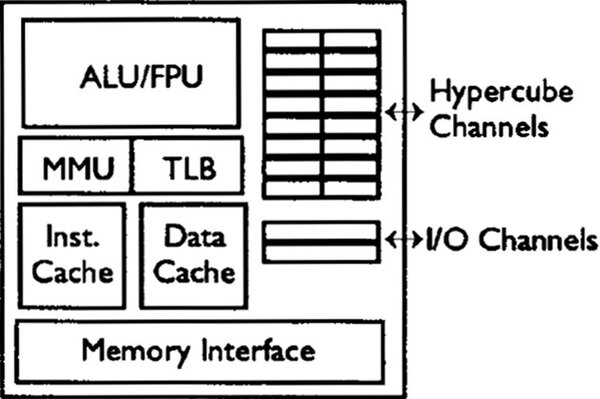

ノードプロセッサーの構成は下の画像の通りである。製造プロセスは0.6μmの3層CMOSで、初期ロットで50MHz、後期ロットでは66MHz動作が可能だった。総トランジスタ数は270万とされている。

ALUはほぼ1命令/サイクルで動作しており、50MHz動作で50MIPS、一方FPUはMAC(Multiply and ACcumulate)命令をサポートしており、つまり1サイクルで乗算と加算を行なえる構成になっており、ピーク性能では50MHz動作で100MFLOPSという計算になる。

これを支えるため、16KBの命令キャッシュおよびデータキャッシュ(どちらも2-way assosiative)を搭載しており、プロセッサー内部のキャッシュの帯域は合計1.6GB/秒とされる。

さすがにこの頃になると、プロセッサー内部もパイプライン化が完了したようであり、特にload/storeは独立したパイプラインで実行することで効率化を図っているという記述がある。

ちなみにスーパースカラーを実装、とする資料もあるが、nCUBE社の論文にはそれを伺わせるものはない(否定する記述もないが)。

細かいところでは汎用レジスターの数も32に増強されており、当然ながらここまで内部構造が変わったため、nCUBE 2とのオブジェクト互換性はない。

→次のページヘ続く (高速転送を可能にしたパラチャンネル)

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ