待機時の消費電力を削減する

PCI Express 3.1

世代的にはPCI Express Gen3に相当するのだが、PCI Express 3.0にいくつかのECN(Engineering Change Notice:技術変更通知)をまとめたものが、近いうちにPCI Express 3.1としてリリースされる予定だ。とはいえこのPCI Express 3.1に内包される主要なECNはすべてPCI-SIGが公開しており、誰でも参照可能である。

横道にそれるが、PCI-SIGのリリースしているスペックそのものは、PCI-SIGのメンバー企業のみが閲覧可能で、メンバー外の人間が購入しようとするとべらぼうに高いのだが、なぜかECNは無償で誰でも入手できるという不思議なポリシーになっている。

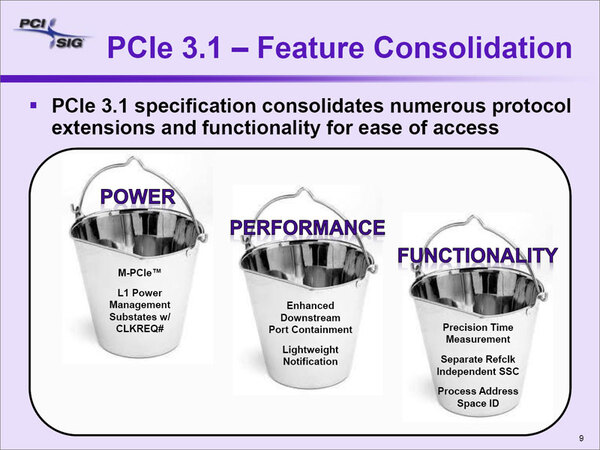

さて話を戻すと、このPCI Express 3.1で追加された主要なECNは上の画像の通り3カテゴリーで計7つほどになる。まず最初は消費電力に関するもので、M-PCI Express、それとL1 Power Management substates with CLKREQ#という2つからなる。

次がパフォーマンスの改善で、Enhanced Downstream Port ContainmentとLightweight Notification。最後が機能の追加で、Precision Time Measurement、Separate Refclk independent SSC、Process Address Space IDの3つとなる。

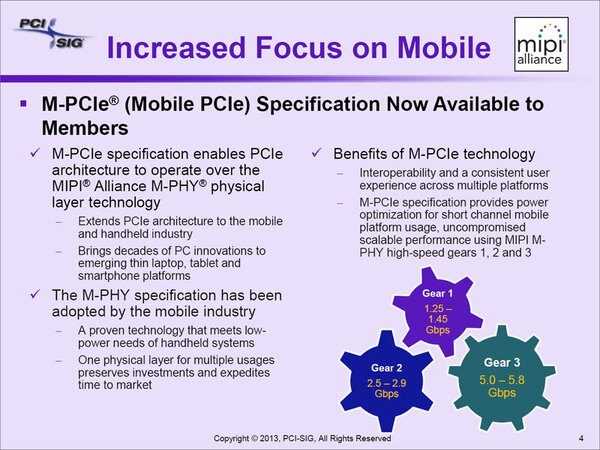

まずM-PCI Expressであるが、これはMIPIアライアンスのM-PHYの上にPCI Expressを実装するというものである。M-PHYは携帯電話などに向けたもので、消費電力の制約が厳しい代わりに配線長は短く、必ずしも高速でなくてもいい接続に最適化されたものである。

M-PCI Expressでは、論理層までは既存のPCI Expressのままで、物理層のみをM-PHYに置き換えたものとなる。ただそのまま単純に置き換えは出来ないので、間にGlue Logic(繋ぎ合わせ回路)を挟み込む形となっており、このGlue LogicがM-PCI Expressとして規定されている。

実のところ携帯電話向けだとPCIバスはピン数が多すぎるので、これまではUSBなどが多用されてきたが、ぼちぼち速度面できつくなってきた。ところがPCI ExpressではGen1でも2.5Gbpsと高速で、信号レベルは30cmくらいの距離の伝達に耐えるため、携帯電話にはオーバースペック過ぎる。

そこで、ユーザーのニーズに合わせて転送速度などをコントロールできるように配慮したのである。したがって、M-PCI Expresは携帯電話と一部のタブレットなどがメインとなる。

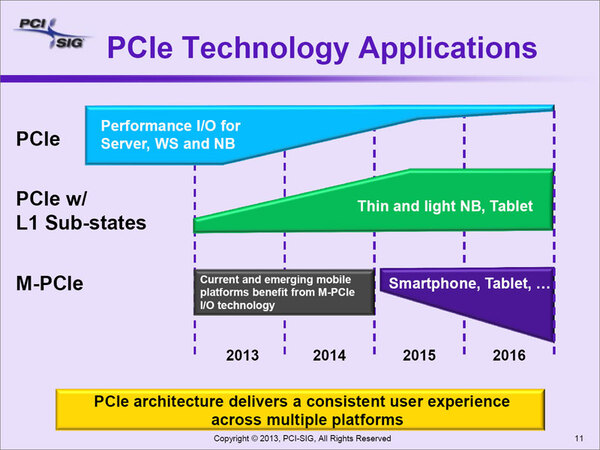

PC向けには、次のL1 Power Management substates with CLKREQ#の方が影響がありそうだ。これはL1 Link StateというPCI Expressのリンク層に省電力動作となるサブステートを設け、通信していないときはこのサブステートに入れるようにすることで消費電力を減らそうというものだ。

このサブステートに入る/出るといった状態管理を、本来はオプション扱いだったCLKREQ#という信号線を使うことになっており、もしもまだCLKREQ#を装備していない場合は追加を求められる。

このECNは、特にノートPCなどでの待機時の消費電力削減に効果的なため、今年から次第に実装が始まり、2015年にはほとんどのノートPCに導入されると見ているようだ。

次がパフォーマンスの改善であるが、これらは一般のケースで、目に見えるほど性能が改善するわけではない。Enhanced Downstream Port Containment(eDPC)はエラーが発生した時に、それを効率よく扱うための仕組みを追加したものだ。

Lightweight Notification(LN)はデバイスからホスト側のキャッシュされたメモリーアドレスを高速にアクセスするためのプロトコル追加である。このLNは、特にGPGPUなどを利用して処理している際に、デバイスから高速に同期を取る時などに有用であろう。

最後の機能追加であるが、Precision Time Measurementは名前の通り、PCI Express経由で時間測定を高精度に行なうための拡張だ。Separate Refclk independent SSC(SRIS)はホストとデバイスで異なるリファレンスクロックの信号を使うための拡張である。

Process Address Space ID(PASID)は、PCI Expressで利用されるトランザクションパケット(TLP)に、新たに20bitのPASIDを追加するものだ。このPASIDを使って、1つのデバイスを複数のプロセスから共用できるようにするという、PCI Expressデバイスの仮想化環境で有用になる拡張である。

ちなみにSRISの場合、ECNにはっきりと「ここには技術的な要求をまとめたが、実際にこれを可能にするための詳細は含まない」と書いてあり、実装は当分先のことになりそうである。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ