SATA Expressでは高速化のために

デバイス側にコントローラーを配置

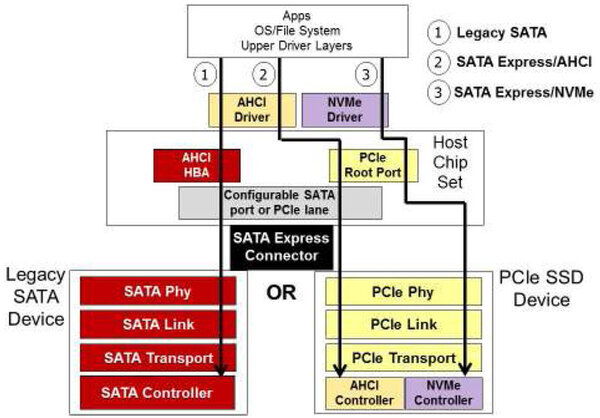

問題は、PCI Expressの上にどうやってSerial ATAのプロトコルを通すか、というより、どうやってPCI Expressデバイスを通常のストレージと認識させるかだ。

これに関してはおもしろい方法で実装される。従来のHDDやSSDはAHCIドライバーからAHCI HBAを経由してSATAで通信するのに対し、SATA ExpressのPCI Expressでは、デバイス側にAHCIもしくはNVMeのコントローラーを配し、AHCIドライバーやNVMeドライバーが直接通信する。

これならばSATAのプロトコルを通す必要はないため無駄なオーバーヘッドがない。AHCIの機能がすべて使えるので既存のOSやドライバー、アプリケーション類に変更は不要である。

欠点としては、PCI ExpressのSSDデバイス側にAHCIやNVMeのコントローラーを改めて追加する必要があることで、これが若干のコスト増の要因になるかもしれない。とはいえ、当面はSATAを使うより高速に接続できるという点で多少価格面でのプレミアを付けられるし、将来的には量産効果でこの分を吸収できるため、それほど大きな問題とはならないだろう。

むしろ問題になるのは、チップセット側のPCI Expressレーンの数になるだろう。SATA Expressの場合、インターフェースは以下のようになっている。

| SATA 3.2が要求するインターフェース | ||

|---|---|---|

| 必須 | PCI Express Gen2 | SATA Gen1i/2i |

| オプション | PCI Express Gen3 | SATA Gen3i |

SATA Gen1i/2i/3iというのはSATAの仕様書における表記で、内蔵用(eSATAではない)のSATA 1.5G/3G/6Gbpsをそれぞれ指している。SATAの方はいいとして、問題はPCI Expressの方である。というのはGen2 x1だと500MB/秒でSATA 6Gbpsより遅くなってしまうからで、現実問題として当面はGen2 x2の構成が一般的になるかと思われる。

ただ最近のチップセットはPCIを廃した関係で、すべてのデバイスがPCI Expressで接続されることになるため、チップセットにI/O用のPCI Expressレーンが余ってるとは言いがたく、多数のSATA ExpressデバイスをGen2 x2で接続するのは無理がある。

また将来的にはPCI Express Gen3をサポートしたいと思われるが、このためにはCPUとチップセット間の接続もPCI Express Gen3以上にしないと帯域的にマッチしない。これらのことから、ここ1~2年の範囲で言えば、SATA Expressデバイスのサポートは1台か多くて2台に限られるであろう。

SATA Expressの

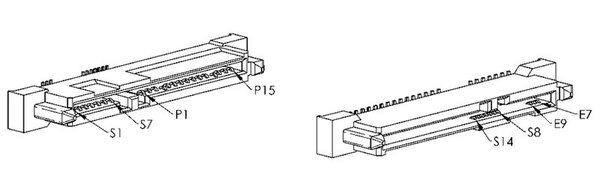

コネクターの形状

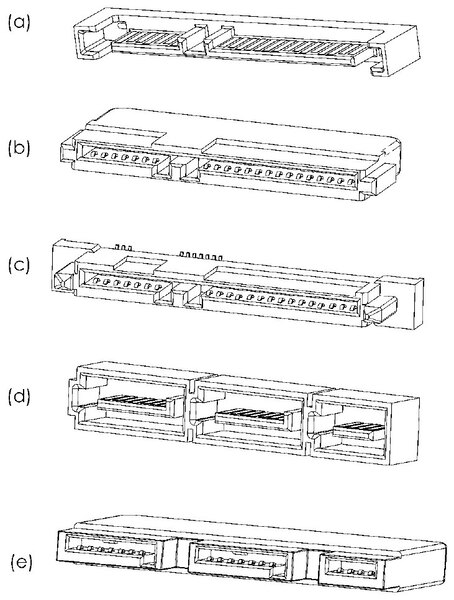

SATA Expressでは当然ながらコネクターの構造が変わる。上図がホスト側レセプタクル(マザーボード上に実装されるコネクター)、下図がデバイス側のコネクターとなる。

デバイス側のコネクターが色々あるのは、ノートPCのように基板に直結するタイプと、ケーブルで繋ぐ従来の方式、さらにホットプラグ(電源オンの状態でSATA Expressデバイスを着脱)にも対応するためである。どのコネクターとどのレセプタクルが組み合わされるか、という一覧はSATA-IOのウェブサイトにあるので、興味ある方は確認していただきたい。

ちなみに仕様上は、SATA Expressを利用してPCI Expressデバイスを作ることも可能ではあるが、現実問題としてそうしたデバイスがどの程度出てくるのかは現状ではわからない。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ