特異な構造と動作モードを持つi860

当初は「Intel 80860」という名前で呼ばれていたこの製品。途中から「i860」に名前が切り替わり、1989年にチップの出荷が開始された。ちなみにi860と並行して、もうひとつのRISCベースCPUである「i960」も開発されている。実はi960の方が先に出荷されているのだが(1985年に完成して1986年に出荷)、こちらは別の黒歴史化しているので、次回にご紹介したい。

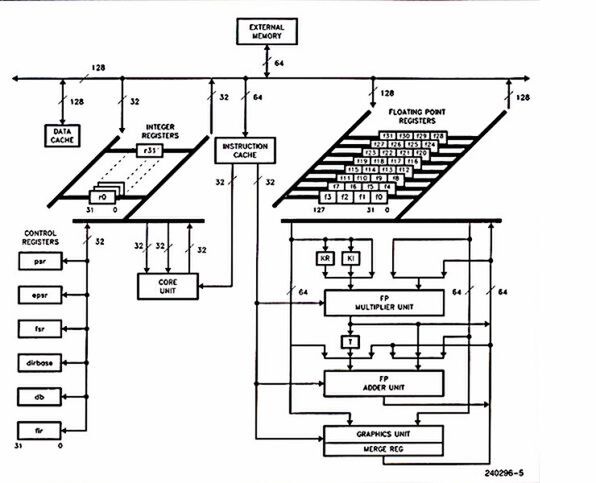

i860のアーキテクチャーは、なかなか特異な構造であった。i860内部は以下の9つのユニットがあり、下の図のような構造で接続されていた。

- Core Execution Unit(整数演算)

- Floating-Point Control Unit(浮動小数点演算制御)

- Floating-Point Adder Unit(浮動小数点加算)

- Floating-Point Multiplier Unit(浮動小数点乗算)

- Graphics Unit(グラフィックス処理)

- Paging Unit(メモリーのページング制御)

- Instruction Cache(命令キャッシュ)

- Data Cache(データキャッシュ)

- Bus and Cache Control Unit(バス/キャッシュ制御)

整数演算は32bitだがFPUは64bitであり、しかもFPU用のレジスターは128bit幅になっている。これに合わせて、内部バスは基本128bit幅である。

整数演算ユニットと浮動小数点加算/乗算が、別々のパイプラインとして構成されているというのも特異であるが、これを制御する命令体系はさらに特異である。i860には「Dual-Operation Instruction」というモードが用意されており、これを使うと、整数演算演算と64bitの浮動小数点演算を同時に行なえる。いわゆるMIMD(Multi-Instruction、Multi-Data)で、命令フォーマット的にはVLIWになる。

その浮動小数点演算は、さらに「Pipelined Mode」と「Scalar Mode」という2種類の動作モードを持つ。Pipelinedモードはいわゆる通常のプロセッサーパイプラインであり、例えば5段のパイプラインなら、5つの連続した命令が順次パイプラインの中で処理される。

一方のScalar Modeでは、ひとつの命令処理が終わるまで、次の命令のフェッチにかからないという、「非」パイプライン動作をする。ほとんどの浮動小数点演算は両方のモードをサポートしているが、一部の命令はScalar Modeのみで動作する。

さらに特異なのは、パイプラインの各ステージの状態を、ソフトウェアから確認できることだ。「PSR」(Processor Status Register)や「EPSR」(Extended Processor Status Register)、「FSR」(Floating-point Status Register)といった制御用のレジスターには、パイプラインの各ステージで問題があった場合に、細かくその状態を示すビットが用意されていた。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ