メモリー編の6回目は、期待を集めながらもはかなく消えた「FB-DIMM」(Fully Buffered DIMM)について解説しよう。

高速化するメモリーで顕在化する

信号波形の減衰問題

FB-DIMMのアイデアは、前回解説した「Registered DIMM」をさらに一歩進めたものと考えればいい。Registered DIMMはAddress/Commandをバッファを介してメモリーチップに送ることで、より多数のDIMMをまとめてつなげられるようにするというアイデアであった。

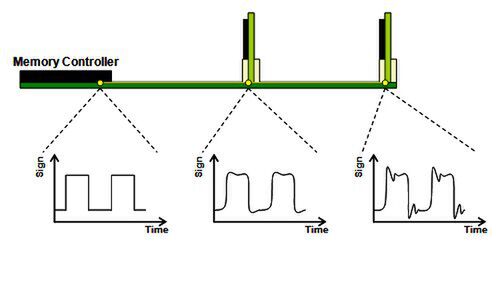

しかし、信号速度がさらに高速化されるとAddress/Commandのみならず、データ信号に関しても精度を維持するのが厳しくなってきた。図1はこれをわかりやすく(実際よりもやや誇張して)示したものだ。基板の上にメモリーコントローラーと2枚のDIMMが装着されたケースを想定している。

メモリーコントローラーから出た時点の信号は、ちゃんとデジタル信号らしくなっているが、1枚目のDIMMの根元で測定すると、信号はだいぶ鈍ってくる。2枚目になると信号の変動はより大きなものになる。これはもっぱら速度に起因する問題である。

DDR-SDRAM世代では「1チャンネルあたりDIMM3枚」という構成がPCでも可能だったが、DDR2-SDRAM世代以降では「1チャンネルあたりDIMM2枚まで」に制限され始めた。これは、特にデータの速度が高速になると、3枚以上のDIMMでは信号の変動が大きくなりすぎてしまうという問題によるものである。

この信号の変動については、もちろんいろいろと対策はある。有名なところでは、あらかじめ信号に「Pre-Emphasis」を施して送り出すとか、受信側で補正を掛ける(イコライザー)といったものである。

Pre-Emphasisとは、ようするに信号の事前補正のことだ。メモリーコントローラーから整った矩形波を送っても、2枚目のDIMMでは大幅に波形が崩れることはわかっている(図2の上段)。この波形を整った形にするには、あらかじめ崩れる波形と逆位相になるような信号を送ればよい。図2中段の赤線で示されているのがそれだ。この波形を送り出すと、2枚目のDIMMでは整った波形が出現することになる(図2下段)。

逆にイコライザーは、波形が乱れて届くことを前提として、その乱れ方から元の波形を再現する機構とでも考えればいい。

問題なのは、こうした手段があまり実用的ではないことだ。例えばPre-Emphasisの場合、2枚目のDIMMにあわせて波形を補正すると、1枚目のDIMMでは逆方向に変化した波形になってしまう。複数枚のDIMMがひとつのメモリーチャネルにつながっている構造では、あまり強力なPre-Emphasisを施して信号を送り出すと、かえってトラブルの元になる。

またイコライザーは、メモリーコントローラーのようなロジック回路に組み込む分にはそれほど難しくないが、DRAMチップは元々そうした複雑な回路を組み込むことを前提にしたプロセスではない。そのため実装は困難だし、コストもかなり上がると考えられるため、これも得策ではない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ