今回は前回に引き続き、メモリーに使われる技術について解説したい。まずは「Registered DIMM」について解説しよう。

メモリーチップやパリティを追加しても安定動作

Registered DIMMの仕組み

例えばサーバー向け用途の場合、「マルチバンクのメモリーを多数実装したい」というニーズは多い。サーバー向けのアプリケーション(例えばデータベースなど)の場合、メモリーの速度やレイテンシのわずかな差よりも、とにかくメモリーの搭載量がそのまま性能に直結しがちだ。そのため「積めるだけ積みたい」というニーズが多く、これに対応する必要がある。

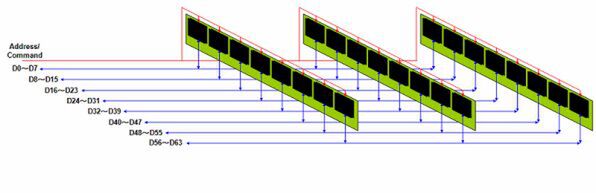

ここで問題となるのは、既存のDIMMを複数枚装着した場合の、信号ラインの負荷である。図1は3枚の「Non Parity 1-Bank DIMM」を装着したケースを想定したものだ。ひとつのメモリーチップが8bit分のデータ幅をサポートするので、8個のチップで64bitになる。

図の「D0」~「D63」はデータバスで、3枚のDIMMを装着すると1本の信号ラインに3個のメモリーチップがぶら下がる計算になる。この程度ならそれほど問題はない。これが2バンクに増えると6個がぶら下がることになるが、それでもまだ問題にはならない。問題なのは、赤で示した「Address/Command」線の方だ。

Address/Command線はひとつのDIMMの中でさらに分岐するので、図1のケースでは8×3=24個のメモリーチップに信号を渡す必要がある。これがパリティ付の場合は27個に増えるし、それが2バンク構成だと54個にもなる。Address/Command線が駆動すべきメモリーチップの数は、データバスに比べて猛烈に多いわけだ。

その結果として、1枚や2枚のDIMMなら動くが、3~4枚やマルチバンクタイプのDIMMを利用するケースなどで動作がおかしくなる、という現象が生じることになった。

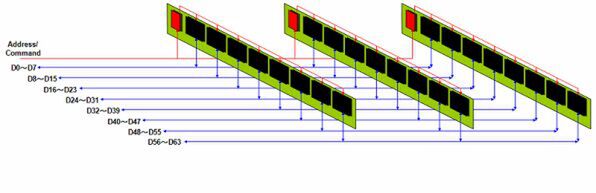

これに対する解決策が、「DIMM上にレジスター(バッファ)を置き、ここで信号を整えてやる」というアイデアだ。図2のように、DIMM上に小さなレジスターを置き、Address/Commandの信号をいったんここで受ける。そしてレジスターから各メモリーチップに分配する。これにより、Address/Commandの信号はDIMMあたり1個のレジスターのみを駆動すればいいので、データバスと同じ条件になるわけだ。

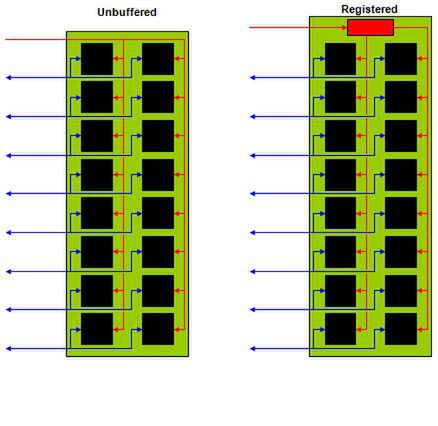

このレジスターを搭載したタイプのDIMMを「Registered DIMM」、逆に搭載しないDIMMを「Unbuffered DIMM」と呼ぶ。Registered DIMMではパリティの有無やバンクの有無も、バッファから先の問題になる。そのためAddress/Command線もデータバスと同じ条件になり、バンクの増加やパリティの影響も受けなくなった。むしろデータバスはバンクの数に合わせて駆動するメモリーチップの数が増えるのに対し、Address/Commandはレジスターがまとめるおかげで数が増えない。だからバンクに関しては、Registered DIMMの方が有利になっているとも言える(図3)。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ