メモリー編2回目では、DRAMから「EDO DRAM」までの進化を説明した。3回目ではそれに続く「SDRAM」の進化を解説したい。

RAS/CASをクロック信号で置き換えたSDRAM

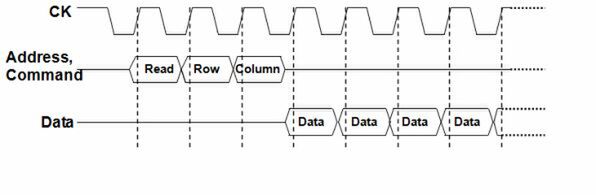

連載94回でも触れたが、SDRAMでは信号線にクロック信号が追加され、これに合わせてデータ転送が行なわれるようになった。図1はその大雑把なリードサイクル図である。

前回も掲載したEDO DRAMの図2と見比べればわかるが、SDRAMでは「RAS/CAS」の信号線が必要ない。EDO DRAMまでは、アドレスがどのタイミングで送られるかを判断するために、RAS/CASを独立した信号線として必要だった。

SDRAMではクロック信号の立ち上がりでアドレスが送られる仕組みになっているので、RASやCASといった信号線でタイミングを取る必要がなくなった。これによるメリットは2つある。まずメモリーコントローラーの側のメリットとして、DRAMのタイミングに合わせて細かく信号線の上げ下げをする必要がなくなったことが挙げられる。

ちょっと込み入った話になるが、CPUのみならず、チップセットやそのほかの周辺回路を含む大規模なロジック回路は、「同期回路」と呼ばれる方式で設計されるのが普通だ。これはクロック信号に合わせてロジック回路の中の細かいブロックが動作し、ブロック間でデータのやり取りを行なう方式である。

ところがEDO DRAMまでは、信号線がクロック信号と無関係なタイミングで上げ下げされることになりがちで、これを標準的な同期回路で処理するのは面倒だった。それがSDRAMになると、メモリーの信号そのものが同期信号になるから、難しい問題もなくメモリーコントローラーを同期回路で設計できるようになった。

一方メモリーの側も、これによって結果的に高速化が可能になった。というのは、SDRAMでは内部の回路を(CPUなどと同じく)パイプライン化することが可能になったからだ。また同時にパイプライン化により、アドレスバスをコマンドバスと共用にすることが可能になった。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 - この連載の一覧へ