Z68が抱える問題はオーバークロック?

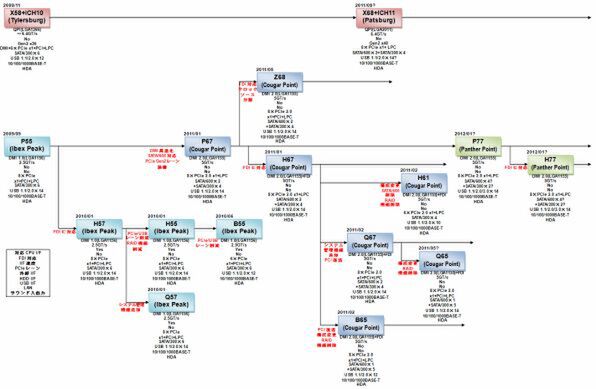

これらに続いて登場する製品であるが、まず2011年5月頃までに、「Intel Q65」と「Intel Z68」が登場する予定だ。Q65はQ67の低価格版であり、基本構成はQ67と同じだが、B65同様に機能の削減が行なわれている。

- SATAポートが6Gbps×2+3Gbps×4から、6Gbps×1+3Gbps×5に削減

- RAID 0/1/5/10のサポート削除

- PCIバスのサポート追加

見てのとおりQ67の低価格版と言うか、B65にIntel AT/AMT 7.0のサポートを追加したと言うべきか、ようするにB65のビジネス向けバージョンと考えればいい。

大きな話題はZ68の方だ。Z68は基本的に「H67のオーバークロック対応版」または「P67のCPU内蔵グラフィックス対応版」とでもいった扱いの製品だ。しかし、例えばデュアルグラフィックス対応などは、実際のPCIe x16レーンはチップセット側でなくCPU側から出ているのだから、本来はチップセットには関係ない話である。これはメモリーもそうで、「H67だからできない」という技術的な問題は本来存在しない。

つまり、これは単に製品差別化の問題であって、単にCPUが起動するときのチップセット内部レジスターの初期設定値が、P67とH67で異なるというだけの話でしかない。そのためH67にオーバークロック動作やデュアルグラフィックス機能を付加するのはそう難しくない。それより大きな話題になっているのはClock Sourceの問題である。

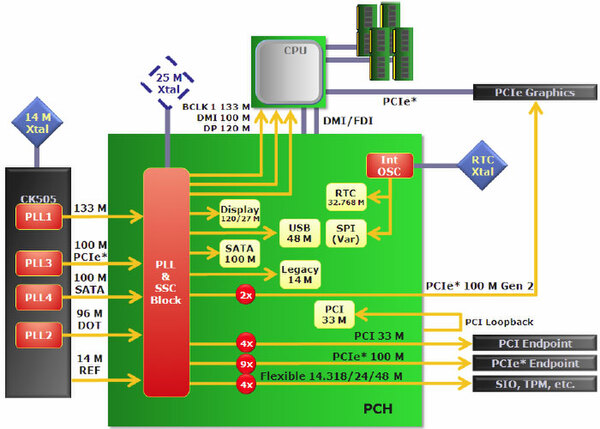

左の画像はIntel 5シリーズの、右の画像はIntel 6シリーズのクロック周りの構造である。Intel 5シリーズは「CK505」と呼ばれる外部PLL(Phase Locked Loop)を必要としていた。このCK505が複数のクロック信号を生成してチップセットに供給し、これがさらにCPUやその他の回路に供給されることになる。このCK505というのは製品名というよりは規格名というべきで、さまざまな会社がこのCK505に対応したクロックジェネレーターを発売している。

だがこうした外付けチップを付けると、どうしても部品コストがかかってしまう。そのためP67/H67では、右画像のように外付けのCK505を廃止。その代わりに25MHzのクロック信号をチップセットに入力して、これを内部のPLL&SSC Blockで分周したり倍周したりという形ですべてのクロック信号を生成するように変わった。一応互換性を保つため、従来のCK505からの信号を受ける端子は用意されているが、実際の説明書を見ると、これらの端子は「Unused」(未使用)と明記されている。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ