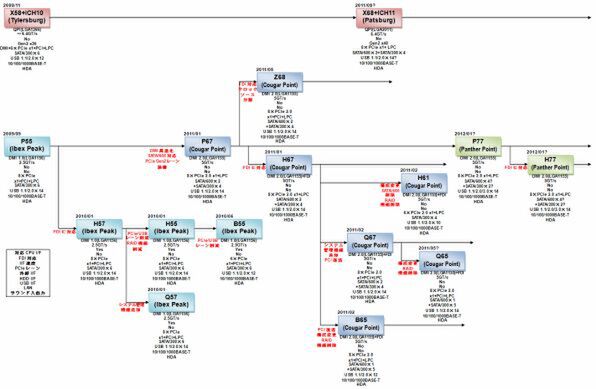

CPU各種のロードマップアップデートに続いて、今回はインテルのチップセットロードマップをアップデートしよう。こちらも以前の解説から丸1年経過した。まずはデスクトップ向けについて解説しよう。

性能面でも改善されたIntel 6シリーズ

連載35回の解説は、ちょうどIntel 5シリーズチップセットがリリースされた直後であった。ロードマップ図では5シリーズも記しているが、前回との相違点は1ヵ所だけである。35回では「Intel Q57」の低価格版について、名称を「Intel Q55?」、登場時期を「2010年5月?」と記していた。実際にはQ57ではなくH57の廉価版という扱いで、最終的に「Intel B55」という名称になり、正式発表は2010年6月1日となった。

5シリーズの次は、「Intel 6」シリーズチップセットである。まず2011年1月に、「Cougar Point」こと「Intel P67」「Intel H67」チップセットが発表になったが、わずか1ヵ月で全量リコールになったという話は、たっぷりニュースになっているので読者の皆様もよくご存じであろう。

すでに問題を修正した「B3 Stepping」のP67/H67の出荷が開始されており、一部のメーカーはマザーボードの交換や、B3 Steppingを搭載した製品の出荷を始めている。1月に登場したSandy Bridgeの盛り上がりは、この問題で出鼻を挫かれた感はあるものの、なんとかリカバリーに向けて推移しているといったところか。

このIntel 6シリーズチップセット、USB 3.0の統合は完全に放棄しており、こちらは次の「Panther Point」こと7シリーズチップセットに持ち越しとなった。とはいえ以下のような改良が導入されており、特に最後の項目はUSB 3.0のチップを接続する際に非常に重要となる。

- SATA 6Gbpsに対応したSATAポートを2ポート内蔵。

- DMIがPCI Express(PCIe) Gen2相当の「DMI 2.0」に切り替わる。

- チップセット側のPCIeレーンも、従来の「なんちゃってPCIe Gen2」から「本当のPCIe Gen2」になった。

ところで、上の何が「なんちゃって」なのかという話だが、Intel 5シリーズの場合、PCIeポートは「PCI Express Base Specification Revision 2.0」準拠をうたっているが、転送速度そのものは片方向あたり2.5GT/秒でしかない。Base Specification Revision 2.0は2.5GT/秒と5GT/秒の両方をサポートしているし、5GT/秒準拠が必須というわけではないから嘘は言っていない。だが、2.5GT/秒どまりなら、「Revision 1.1相当」というのが正しい言い方ではないかと思う。

それがIntel 6シリーズでは片方向あたり5GT/秒と、今度こそ正しくRevision 2.0準拠となっている。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ