パイプラインハザード対策には、分岐予測やパーシャルフラッシュ

これを補うための方策として広く利用されているのが、分岐予測機構である。パイプラインハザードは要するに、「間違った方向の命令をデコードするから発生する」とも言えるわけで、正しく命令をデコードすればこうした事態は防げる。そこで、デコードの際に分岐命令を発見したら、「次にどちらの方向に分岐するか」をきちんと判断して次の命令を決める仕組みが、今のCPUには搭載されている。

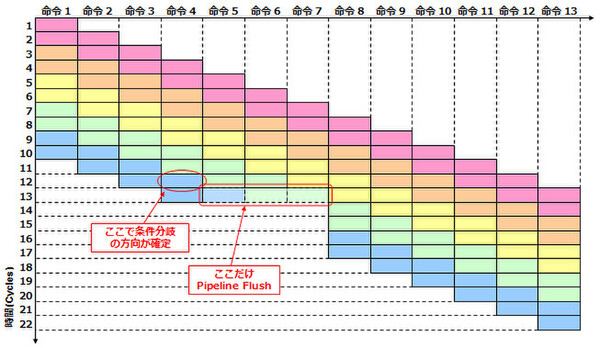

また「パーシャルフラッシュ」と呼ばれる仕組みを搭載しているものもある。図4では分岐ミスが発生した場合、パイプライン全体をフラッシュしていた。しかし図4の場合、間違っているのは命令5~7までの処理で、命令8以降はそのまま継続しても問題ない。そこで、命令5~7を処理しているステージのみフラッシュすることで、パイプラインハザード時のペナルティを軽減しようというものだ。

実際図5の場合、ペナルティは3サイクル分で済んでいる。もっともこの機構は単純なパイプラインでは実装しやすいが、さまざまなテクニックを駆使している昨今のパイプラインでは、機構的に複雑になりすぎてしまうため実装されないこともある。

ほかにも、分岐ミスが発生することを前提に、発生した場合のペナルティを軽減する仕組みがある。Decodeで分岐を確認した場合、その分岐先を2つとも内部のテーブルに格納しておくというものだ。これにより分岐ミスが発生した場合も、ただちに次のデコードを開始できる。

もっと積極的な方法としては、「投機実行」という仕組みを実装しているCPUもある。例えばインテルのItaniumだ。図3では、命令4のどちらか片方だけを実行するから、外れた場合にペナルティが大きい。それならば、命令4の後に命令5/6/7と命令8/9/10の両方を同時に処理をしておき、命令4の結果が確定した時点で、間違った分岐の結果を捨てるという、Partial Flushをもっと積極的に行なうような仕組みだ。ただこれはCPUが複雑になりすぎることもあって、採用例はほとんどない。

パイプラインの問題とそれをカバーする技術をざっとおさらいしたところで、次回は別の高速化技法である「スーパースカラー」について紹介したい。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ