アナログ・デバイセズ(株)は9日、都内で記者発表会を開催し、3G携帯電話の無線基地局(Node B基地局)(※1)向けのベースバンド処理向けDSP『TigerSHARC ADSP-TS101S』を発表した。従来の2チップ構成の回路に比べ、チップコストが半分になるという。

※1 Node B基地局は、端末機との無線接続を行なって交換基地局に接続する役目を持つ局。3G携帯電話システム向けNode B基地局は現在仕様の策定中。 |

|---|

| 『TigerSHARC ADSP-TS101S』 |

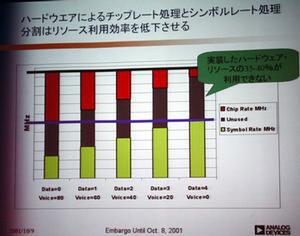

TigerSHARC ADSP-TS101Sについて説明した、米アナログ・デバイセズ社ワイヤレス・インフラストラクチャ・グループ、プロダクトライン・ディレクターのケビン・ラリー(Keven Leary)氏によると、3G向けNode B基地局のベースバンド処理は、これまではカスタムASIC(特定用途向けIC)とDSPの組み合わせや、FPGA(Field Programable Gate Array)で行なうのが一般的だったという。ただこの方法では、ベースバンド処理に含まれる主要な2つの“チップレート処理”(※2)と“シンボルレート処理”(※3)を別々にこなす必要があった。この2つの処理は、一方が重いときはもう一方は軽い、といった相反する処理だが、2つの処理の回路とも、最も重い処理がこなせるようにするため、常に利用しない処理能力が35~40%程度あるという。カスタムASICやFPGAは高価な部品であり、さらに外部に高速で高価ななメモリーを必要とするため、コスト削減の妨げとなってしまい、通信事業者からの低コスト化の要求に必ずしも応えられていないという。

※2 3G携帯電話、cdmaOne方式携帯電話の基本となるCDMA(符号分割多重接続)データ処理※3 エラー検出や訂正のために符号化して送出するデータ処理

|

|---|

| 米アナログ・デバイセズ社ワイヤレス・インフラストラクチャ・グループ、プロダクトライン・ディレクターのケビン・ラリー氏 |

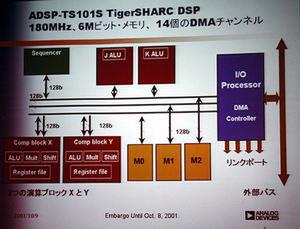

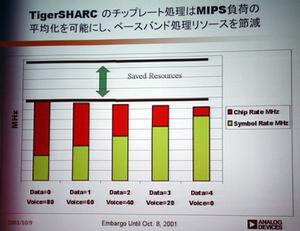

アナログ・デバイセズが今回発表したTigerSHARC ADSP-TS101Sは、通信事業者と協力して開発したもので、チップレートとシンボルレート処理の専用命令を組み込んだ。また6Mbitのメモリーを内蔵し、TigerSHARC ADSP-TS101Sのみでベースバンド処理が行えるようにした。動作周波数は180MHzで、外部ロジック回路なしで、複数のTigerSHARCを組み合わせたマルチプロセッシング構成を取ることも可能。チップレート処理とシンボルレート処理において、DSPの処理能力を動的に割り当てられるため、リソースの利用効率も高いとしている。パッケージは安価な業界標準パッケージとして19×19mmのPBGA(プラスチック ボール グリッド アレイ)を採用する。Node B基地局ではシステムコスト低減のため、ヒートシンクやファンが利用できないが、TigerSHARC ADSP-TS101Sの消費電力は1W以下に抑えており、熱設計にも有利だとしている。

|

|---|

| TigerSHARC ADSP-TS101Sのブロック図 |

また、3G携帯電話においては、日欧では“W-CDMA”、米ではW-CDMAと“cdma2000”、中国では“TDS-CDMA”と、地域によって方式が異なるが、TigerSHARC ADSP-TS101Sでは、基本的にはソフトウェアのみの対応によって、回路を再設計しなくとも対応が可能という。このことは、従来のFPGAなどに比べて開発期間の短縮にもつながるとしている。TigerSHARC ADSP-TS101Sの価格は10万個ロット時75ドル(約9000円)となっている。

|

|---|

| カスタムASICとFPGAなどで構成したベースバンド処理の場合 |

|

|---|

| TigerSHARCによるベースバンド処理。ハードウェアリソースの利用効率が良く、コストが抑えられるとしている |

本記事はアフィリエイトプログラムによる収益を得ている場合があります