チップの上に直接DRAMを積層することで

メモリー帯域とメモリー容量問題の解決を図る

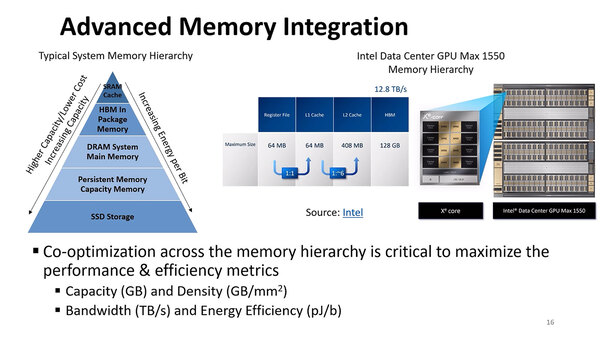

2つ目がメモリーの問題。下の画像が従来のメモリー構成であり、Ponte Vecchioなど4階層のメモリーを搭載しているわけだが、そのPonte Vecchioですらメモリー帯域と容量が足りていないので、もう少し別の方法を考える必要がある。

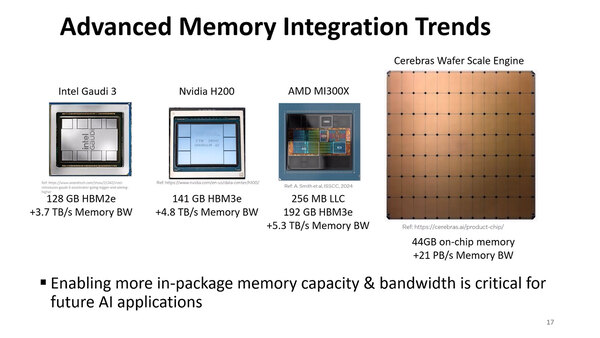

そのPonte Vecchioの後に出てきたAI向けプロセッサーが、いろいろな意味で限界までメモリー量とメモリー帯域を引き上げているのを見れば、この方向でもう少し頑張るしかないわけだ。

一番考えやすいのは、さらにHBMのスタックを積み上げる(=容量を増やす)とともに信号を高速化するなどで帯域を引き上げることだが、これは言ってみれば小手先の改良であって、大きく性能を改善する助けにはならない。

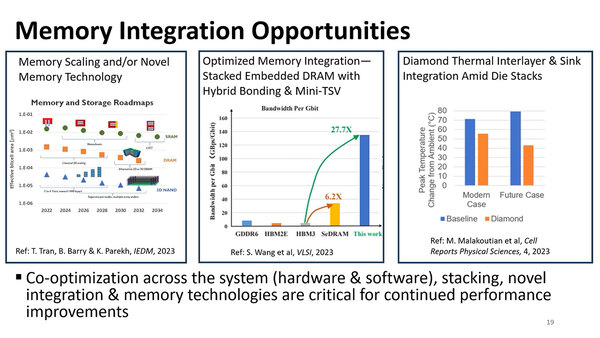

この方面に関して明確な解が示されているわけではないのだが、1つのアイディアとして示されたのがStacked Embedded DRAMである。要するにチップの上に直接DRAMを積層するというアイディアだ。

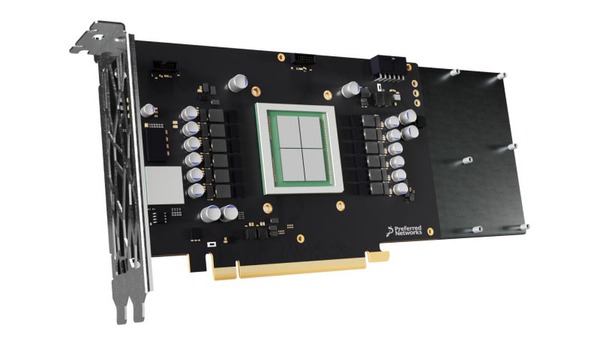

実はこれ、連載798回で取り上げたMN-Core 2の後継であるMN-Core L1000で実装されようとしている。

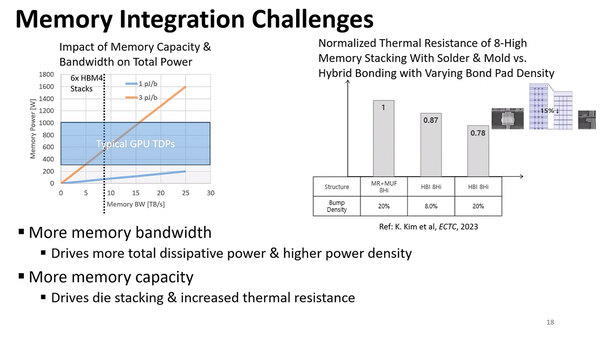

要するにHBMの消費電力が多いのは、インターポーザー経由になっている(つまり先の話で言えばFan Outでの接続になる)部分が少なからず関係する。つまり、DRAMをHybrid Bondingで接続するようにすれば、信号速度を控えめにしても帯域が確保しやすく(これは配線の本数を大幅に増やせるから)、またHybrid Bondingだからインターコネクトの電力も低く抑えられる。

チップの上のDRAM積層に関しては、MN-Coreのアーキテクトである牧野淳一郎博士のXへのポストがなかなか興味深い。

DRAM 3 次元実装についての牧野の https://t.co/kvYWywQzrq 19年前の文章

— Jun Makino (@jun_makino) December 11, 2024

これは、Hybrid Bondingを使う限り熱抵抗が大幅に減るので、DRAMをチップの上に載せても放熱に問題が出にくい、という話である。理屈はわかるのだが、それはロジックダイの発熱が穏当なものの場合だろう。

これがH200や、身近なところではCore Ultra 9でもいいのだが、要するに90度以上で連続動作するような状態ではDRAMの記憶保持時間が相当短くなりそうで心配である。したがってこの手法は、ロジックダイ側の動作周波数を相当低く抑えるか、液冷などで強制的に50~60度に抑え込む必要がありそうではあるが、1つの可能性ではあるかと思う。

コストを度外視すればSRAMを大量に3D実装という選択肢もありそうだが、これは本当にコストが論外になりそうではある。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ