ゲート長6nm、Finの厚み1.7nmのRibbonFETも試作

IEDM 2024でインテルが1枚のウェハーから1万5000個以上のチップレットを数分で切り出す技術を発表

2024年12月08日 05時00分更新

2024年12月7日~12月11日、IEDM 2024が米国カリフォルニア州サンフランシスコで開催する。IEDMとは、International Electron Device Meetingの略で、日本語にすると「国際電子デバイス会議」。毎年、先端半導体技術などの論文が多数提出されているイベントで、今年は70周年の節目になる。

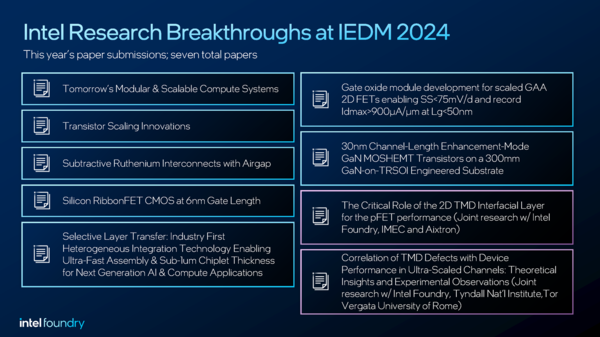

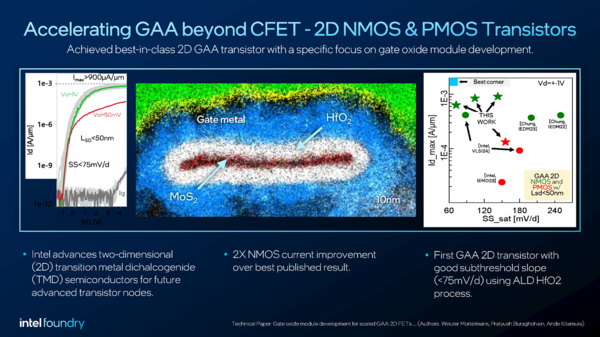

そんなIEDM 2024で、インテルは2本の招待講演と7本の論文を発表する予定だ。報道機関向けに事前説明の機会を設け、インテル・ファウンドリー部門シニア・バイス・プレジデント兼ジェネラル・マネージャー、テクノロジー・リサーチ・グループのサンジェイ・ナタラジャン(Sanjay Natarajan)氏がそのプレビューをいくつか紹介した。

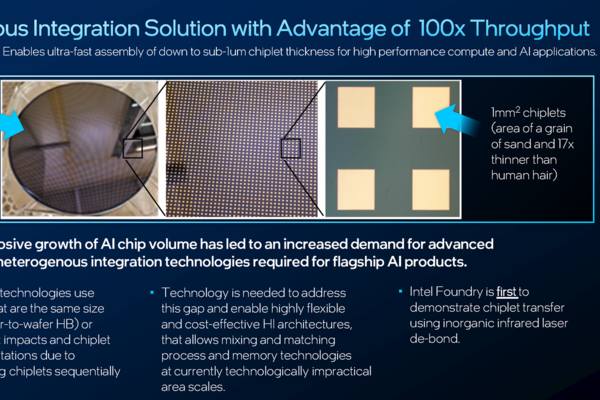

まずはHI(Heterogeneous Integration)技術について。Lunar Lakeなどに代表される近年のCPUは、機能別にさまざまなタイル(チップレット)を作り、それらを組み組み合わせることでより柔軟な製品を開発できる方向がトレンドになってきている。それがHeterogeneous Integration(日本語にすると、"異種統合”)と呼ばれる技術なわけだが、その製造方法においける話題だ。

従来のHIチップレットは、2つのダイを同じサイズと技術にして、ウェハーレベルで張り合わせる(Wafer-to-Wafer。一番安く上がる)か、ウェハーの上に別に製造したチップレットを載せる(Chip-to-Wafer。高価で時間もかかる)かの2種類だった。そんな中、インテルは今回、無機赤外線レーザー(inorganic infrared laser)を利用し、1枚のウェハーの上に構築した1万5000個以上のチップレット(面積:1mm2)を数分でde-bond(分離)できる技術を実証した、としている。

次世代のチップレット積層技術については、よりModularity(モジュール性)が重要であるとし、そこに向けて次世代EMIB(Embedded Multi-die Interconnect Bridge)を用意していることも明らかにした。

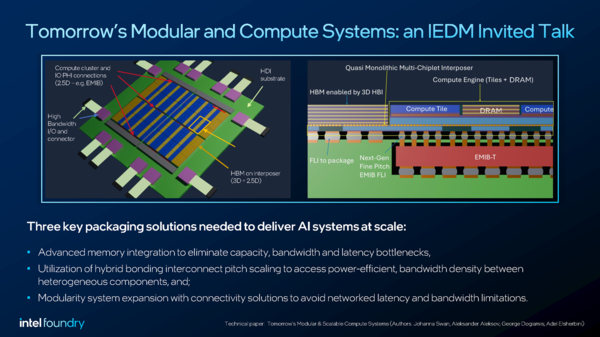

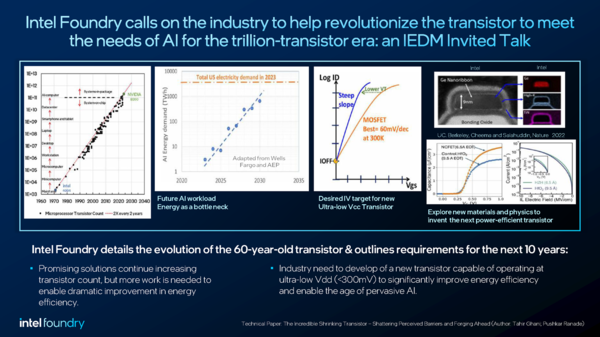

次がトランジスターについて。インテルもIntel 20AやIntel 18A/14AではGAA(Gate All Around)形式のRibbonFETを利用することをすでに明らかにしているが、このRibbonFETについて、ゲート長6nm、Finの厚み1.7nmで高効率なトランジスターを試作したとのこと。

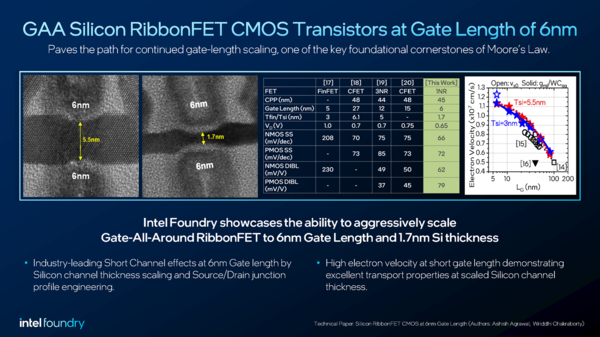

そのGAAについては、二硫化モリブデン(MoS2)の周囲を酸化ハフニウム(HfO2)でカバーする形の電極とすることで、サブスレッショルド特性を向上させられる(75mV/d以上)ことも示された。

おそらくはこうしたトランジスターの改善によって、GAAを利用してまだムーアの法則が維持できるであろう、という見通しが招待講演の2つ目で語られると思われる。

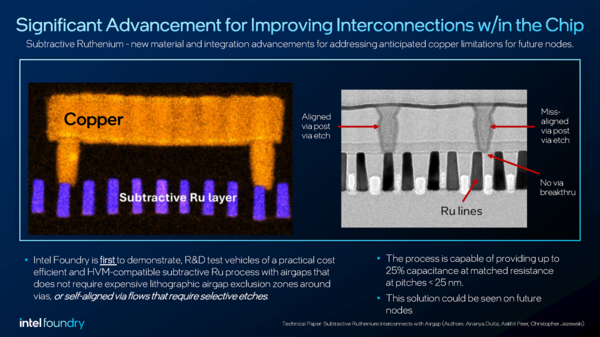

最後がインターコネクトの技術である。現在は銅あるいはアルミがインターコネクトのメインで、部分的にタングステンが使われたり(主にVIA)、コバルトを銅でカバーしたり(主にエレクトロマイグレーション対策)といった具合だが、今回インテルはRu(ルテニウム)ベースの配線層に関する発表を行う。

もともと、国際研究機関のimecなどは2nm世代はRuベースの配線が有望ということで以前から研究を行っており、インテルの発表もこうした流れの一環なのだろう。ただし、上図の右下にもあるように、これは将来のプロセスに向けたもので、直近のプロセスノード向けではない。

というわけで、今回の事前説明は内容の「チラ見せ」という感じ。詳細はIEDM 2024での正式発表を待つことになる。ちなみに、「テクノロジー・リサーチ」は以前「コンポーネント・リサーチ」と呼ばれていたグループで、古めかしい用語だったので改称したという。装いも新たになったインテルの技術革新に期待したい。