ロードマップでわかる!当世プロセッサー事情 第785回

Xeon 6のIOチップレットには意地でもDDR5のI/Fを搭載しないインテルの強いこだわり インテル CPUロードマップ

2024年08月19日 12時00分更新

Xeon 6900シリーズは有機パッケージが2段重ねの不思議な構造

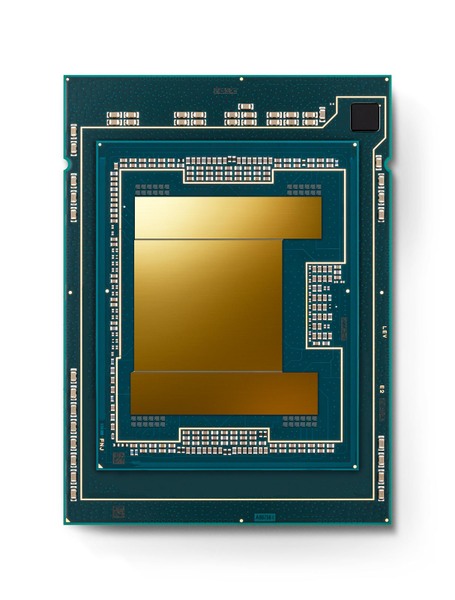

Xeon 6900シリーズの構成が下の画像だ。こちらもXeon 6700シリーズと同様に推定すると下表の構成になっているように見受けられる。

| Xeon 6900シリーズのコンピュート・チップレット内部構造 | ||||||

|---|---|---|---|---|---|---|

| Eコア | Eコア×4のクラスターが6×6構成のメッシュで、上下にそれぞれメモリーコントローラー×3が配される | |||||

| Pコア | Pコアが9×5構成で、3 チップレットで合計7つが冗長コアとなる。上下にそれぞれメモリーコントローラー×2が配される | |||||

ここから察するに、Eコアのコンピュート・タイルはFCLGA 4710のものと共通で、ただしチップレットあたり8chのメモリーコントローラーを6chに制限したもの。またPコアの方はFCLGA 4710のXCCをそのまま流用しているようだ。

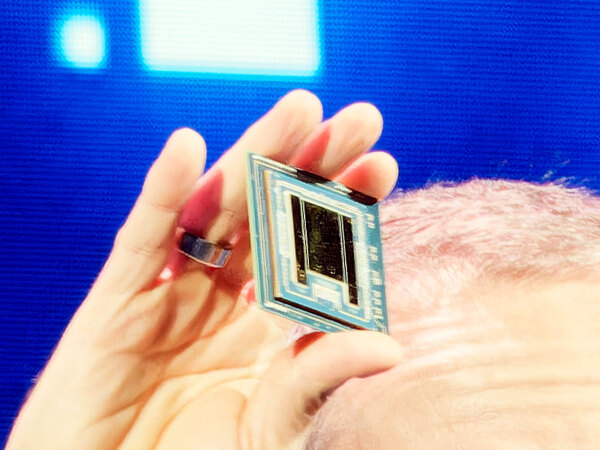

ところでそのXeon 6700、実際のパッケージ写真が下の画像だが、少し妙なことに気がつく。なぜ有機パッケージの2段重ねになっているのだろう?

実際横から見ると、明らかにパッケージが2段重ねになっているのがわかる。理由は不明であるが、こういう構造だと上側のパッケージにコンピュート・タイルを2つ載せるのは絶対に不可能である。それにしても不思議な構造である。

これはCOMPUTEXの基調講演でGelsinger CEOが示したもののアップ。チップの厚みがわかる。少しブレ気味なのはご容赦を。ちなみにTech Tourでは製品サンプルを撮影する機会があったらしいが、COMPUTEX会場での展示はなかった

以上のように、Xeon 6の世代でインテルは5種類(Eコアのコンピュート・チップレット、PコアのXCC/HCC/LCCチップレット、IO チップレット)ものチップレットを製造する必要があることになる。最大の理由は、意地でもIOチップレットにDDR5のI/Fを搭載しなかったためである。

AMDの考え方なら、メモリーコントローラーをIOチップレット側に移動したうえで、Pコア×16のみの細長いコンピュート・チップレットを用意するだろう。XCC向けはこれを5つか6つ。HCCは2つ、LCCは1つである。それにIOチップレットを組み合わせれば完成なのだが、そうしなかったあたりがインテルなりのこだわりだろう。

言うまでもなく絶対性能そのものはインテル方式の方が高くしやすい(本当に高くなるかどうか、はまた別の問題)。ただしそのために多数のチップレットを設計・製造するのでコストは当然高くなるし、チップレットそのものの面積も大きくなるので歩留まりも下がる。

さらに言えば検証するべき組み合わせが増えるということでもある。この検証周りはSapphire Rapidsの時も問題になっていたし、現在進行中でRaptor Lakeの問題(こちらもまだ解決していないというか、本当の原因が判明していない)もある。そこに来て今度はXeon 6の多数の組み合わせの検証が待っているわけで、検証チームの負荷は増えるばかりというのは、お気の毒としか言いようがない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ