ロードマップでわかる!当世プロセッサー事情 第785回

Xeon 6のIOチップレットには意地でもDDR5のI/Fを搭載しないインテルの強いこだわり インテル CPUロードマップ

2024年08月19日 12時00分更新

連載736回の答え合わせ

左と中央がPコアタイル、右がEコアタイルで正解だった

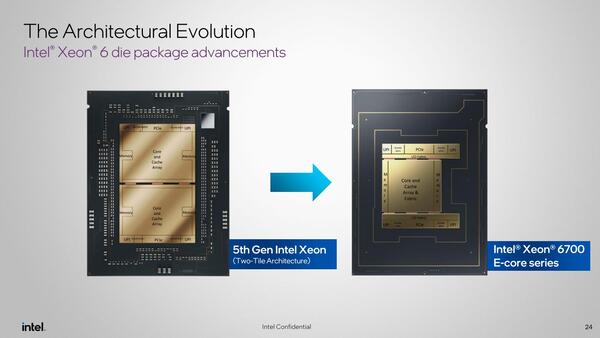

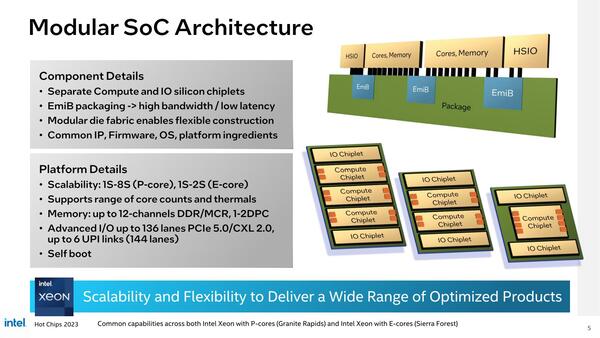

ところで連載736回で、Hot Chips 2023におけるスライドを取り上げたが、これの答え合わせをする時間がやってきた。

連載736回での疑問は以下のとおり。コンピュート・タイルが明らかに2種類あるあたりが謎。左と中央がPコアタイル、右がEコアタイルなのだろうか? それはともかくEMIBの表記が“EmiB”になっているのは、どういうことなのだろう?

まずXeon 6700シリーズ、つまりFCLGA 4710のパッケージが下の画像である。

Eコア(左側)は比較的スクエアなコンピュート・チップレットの両側にIOチップレットが配される格好。以前の情報で言えば、コンピュート・チップレットにメモリーコントローラーが搭載される模様。つまり144 Eコア+8ch DDR5 I/Fである。

Pコア(右側)は、またもやXCC/HCC/LCCの3種類のコンピュート・チップレットが用意される。ということは以下の構成になる。

| コンピュート・チップレット別の構成 | ||||||

|---|---|---|---|---|---|---|

| XCC | チップレットあたり43 Pコア+4ch DDR5 I/F | |||||

| HCC | チップレットあたり48 Pコア+8ch DDR5 I/F | |||||

| LCC | チップレットあたり16 Pコア+8ch DDR5 I/F | |||||

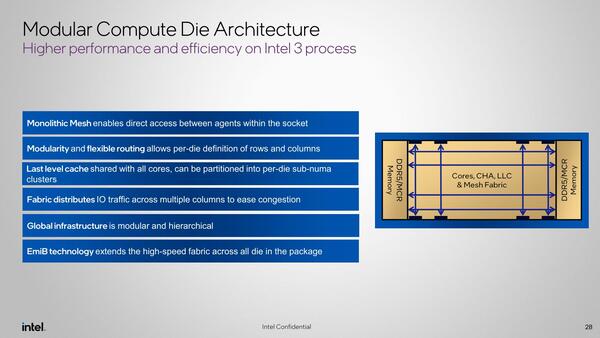

プロセッサー内部の構造が下の画像で、ここから察するに下表のような内部構造になっているように思える。

コンピュート・チップレットにメモリーI/Fを統合したのが間違いだと思うのだが……。それはともかく、コンピュート・チップレットとIOチップレットの間が3ヵ所でつながっているが、おそらくこれはイメージだろう

| Xeon 6700シリーズのコンピュート・チップレット内部構造 | ||||||

|---|---|---|---|---|---|---|

| Eコア | Eコア×4のクラスターが6×6構成のメッシュで、上下にそれぞれメモリーコントローラー×4が配される | |||||

| XCC | Pコアが9×5構成で、うち2つが冗長コア。上下にそれぞれメモリーコントローラー×2が配される | |||||

| HCC | Pコアが7×7構成で、うち1つが冗長コア。上下にそれぞれメモリーコントローラー×4が配される | |||||

| LCC | Pコアが4×4構成。上下にそれぞれメモリーコントローラー×4が配される?(これだけ見ていると、LCCはそれぞれメモリーコントローラー×2で、最大4chに制限されるように思えなくもない) | |||||

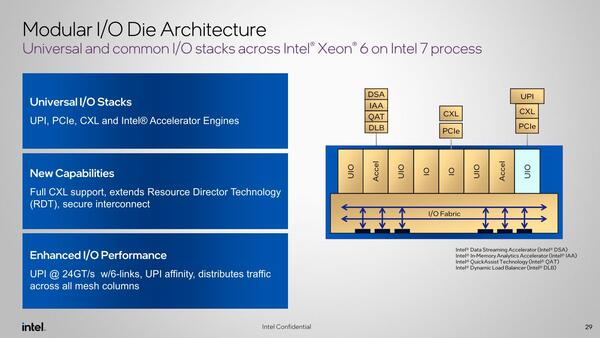

XCCで冗長コアが多いのは消費電力の制限の可能性もありそうだ。一方IOチップレットそのものは、少なくとも今見てる限りはEコア/Pコアで共通に思える。内部構造は下の画像のとおりで、アクセラレーターと外部I/Fをまとめた格好である。

このIOチップレット、最初のページにある2つ目の写真で比較する限りにおいては同じ幅と高さになっており、実際の製品写真での比較ではないので断言はできないがXeon 6900シリーズと共通の可能性が高い。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ