COMPUTEX/TAIPEI 2024におけるAMDの新発表に関しては、すでにKTU氏のレポートCPU編とGPU編が上がっているので御覧になった読者も多いだろう。ここではKTU氏のレポートを補足する形で、いくつか説明を追加したい。

KTU氏のレポートはこちら

2024年6月3日、AMDはCOMPUTEX 2024に連動し基調講演を開催、さまざまな発表を行なった。本稿はコンシューマー向けの製品発表についてまとめたものである。

2024年6月3日、AMDはCOMPUTEX 2024に連動し基調講演を開催した。本稿は、プロフェッショナル向けGPUの製品発表についてまとめたものである。

Zen 4からZen 5に変更されIPCが向上する

Ryzen 9000シリーズ

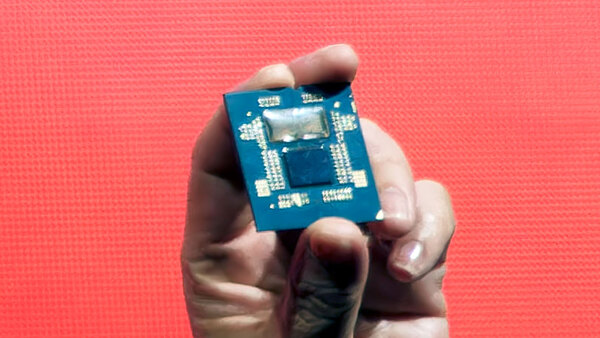

まずは冒頭に出て来たRyzen 9000シリーズ。PackageそのものはAM5であり、既存のAM5マザーボードがそのまま(といってもBIOSアップデートは必要だろうが)利用できる形になるというのは既報の通り。

そんなRyzen 9000シリーズであるが、以下の特徴がある。

- CCDはZen 5ベースに刷新された。製造プロセスは4nm

- IODはRyzen 7000シリーズのものをそのまま利用。なのでTSMC N6での製造

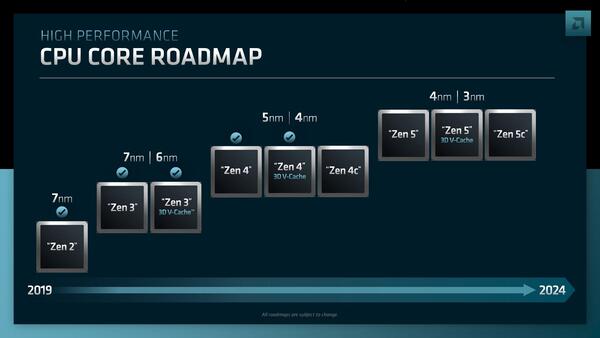

以前AMDが示したロードマップでは、Zen 5世代は4nmと3nmを利用することが明らかにされている。後述する理由で、おそらくZen 5cにあたるものはTurinとしてTSMC N3を利用して製造される一方、RyzenおよびZen 5ベースのEPYCはTSMC N4での製造になるようだ。

ちなみにTSMCのN5とN4はほとんど同じである。TSMCの説明では、N4プロセスはN5プロセスから若干トランジスタ密度を向上した程度であり、N5とデザインルールが互換なので、比較的容易に移行が可能としている。逆に言えば動作周波数向上あるいは消費電力削減の効果はあまり期待できない。

またIODがRyzen 7000シリーズと共通ということは、Ryzen AIは未搭載だし利用できるIGPUの性能にも違いがないことになる。要するに差異はZen 4→Zen 5への変更で、これによりIPCが向上する「だけ」である。

実際Ryzen 9 7950XとRyzen 9 9950XはブーストクロックもTDPも一緒に設定されている。ベースクロックはまだ発表されていないが、おそらく大きくは変わらないだろう。最近のAMDはかつてインテルが採用したTick-Tockモデルに近い動きをしているが、今回はTock(マイクロアーキテクチャーの刷新)に相当すると考えればいい。

そのマイクロアーキテクチャー刷新の詳細は、今回は未発表である。これに関しては、7月に予定されているRyzen 9000シリーズの発表に先んじてTech Dayが開催され、そこで詳細が公開されることになると予告されているので、こちらが明らかになるまでお待ちいただきたい。

AMD 800シリーズチップセットは

B650EのPCIeレーンを強化したもの

Ryzen 9000シリーズはAM5プラットフォームを利用しているので既存のAM5対応チップセットが利用できる。基調講演などで示されたパフォーマンスデータも、脚注を見るとRyzen 9 9950XはX670Eチップセットと組み合わせる形で稼働している。その意味では新しいチップセットはなくても構わないのだが、今回X870EおよびX870が発表された。

この800シリーズチップセットだが、David McAfee氏(CVP&GM, Ryzen channel business)に尋ねたところ、開口一番言われたのが「USB4はディスクリートだ」。つまりUSB4を標準搭載といっても、それはチップセットに内蔵するわけではなく、PCIeレーン経由で外部搭載のUSB4コントローラーに接続するだけという話であった。

だとすると既存の600シリーズとなにが違うのか? という話であるが、McAfee氏曰く「I/Oを強化している。また、600シリーズを出荷してすでに2年が経過しており、これにより配線や基板の構造などに関してより深い知見を得られた。こうしたものをフィードバックしたのが800シリーズ」とのことだ。

要するにもう6層基板を使わずに、安価な4層基板で製造が安定してできるようになった、ということでこれはユーザーというよりはマザーボードメーカー向けのメリットということになる。

ではX870とX870Eの違いは?という話になるわけだが、600シリーズの場合と異なりどちらもPCIe 5.0対応である。実際の違いは? というと、X870Eはアップストリームとダウンストリームの2チップ構成、一方X870は1チップ構成である。要するにB650EのPCIeレーンを強化したものがX870、X870を2つつないだものがX870E、という2つに収まった。

PCIe 4.0のみの構成を排除した理由は、おそらく外付けのUSB4コントローラー接続のためだろう。USB4は片方向あたり40Gbpsの転送速度を持つので、これをPCIe 4.0で接続すると最低3レーン、実質4レーンを占有することになる。これがPCIe 5.0なら2レーンで帯域的に間に合うことになる。フルスピードでなくてよければ1レーンでも32Gbpsまで出るからそこそこには動くだろうが、これをAMD的に認めるとは思えない。

あと現実的に、SSDがぼちぼちPCIe 5.0にシフトし始める(PHISONも今年後半に発熱の少ないPCIe 5.0対応コントローラーをリリースすると明らかにした)ことを考えると、PCIe 4.0版を残してもニーズがないと判断したものと思われる。というより、PCIe 4.0で足りるというユーザーには、それこそB650やX670でも対応できるからだ。

ちなみにKTU氏も言及していた、EXPOメモリー利用時により高い動作周波数が可能になるという話は、チップセットというよりはCPUあるいは基板の配線の方が影響が大きい。McAfee氏の言う「配線や基板の構造などに関してより深い知見を得られた」というのは、このEXPO利用時のオーバークロックに関しての話の可能性もある。つまりチップセット云々というよりは、X870/X870Eを利用したマザーボードは、より高いオーバークロックが可能な配線構造になっている、というあたりが正確なところなのかもしれない。

この連載の記事

-

第777回

PC

Lunar Lakeはウェハー1枚からMeteor Lakeの半分しか取れない インテル CPUロードマップ -

第775回

PC

安定した転送速度を確保できたSCSI 消え去ったI/F史 -

第774回

PC

日本の半導体メーカーが開発協力に名乗りを上げた次世代Esperanto ET-SoC AIプロセッサーの昨今 -

第773回

PC

Sound Blasterが普及に大きく貢献したGame Port 消え去ったI/F史 -

第772回

PC

スーパーコンピューターの系譜 本格稼働で大きく性能を伸ばしたAuroraだが世界一には届かなかった -

第771回

PC

277もの特許を使用して標準化した高速シリアルバスIEEE 1394 消え去ったI/F史 -

第770回

PC

キーボードとマウスをつなぐDINおよびPS/2コネクター 消え去ったI/F史 -

第769回

PC

HDDのコントローラーとI/Fを一体化して爆発的に普及したIDE 消え去ったI/F史 -

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ - この連載の一覧へ