Granite Rapidsのダイサイズは

PHYまで含んでほぼ600平方mm

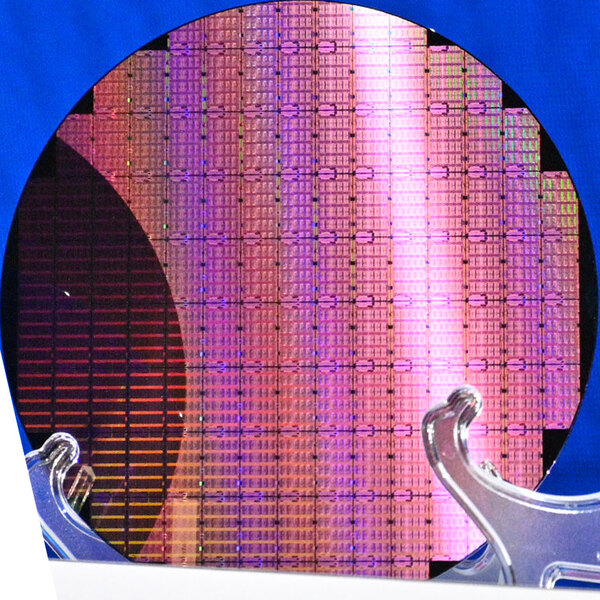

ところで今回の基調講演、壇上には展示されていながら説明されなかったのがGranite Rapidsのウェハーである。

これをむりやり歪み補正したのが下の画像だ。ダイサイズは32.18×18.65mmで599.98mm2なので、ほぼ600mm2となる。

連載736回ではコア部だけで600mm2程度、周辺のPHYも合わせると700mm2を切る程度と想定したが、実際にはPHYまで含んで600mm2以内に収まった格好だ。

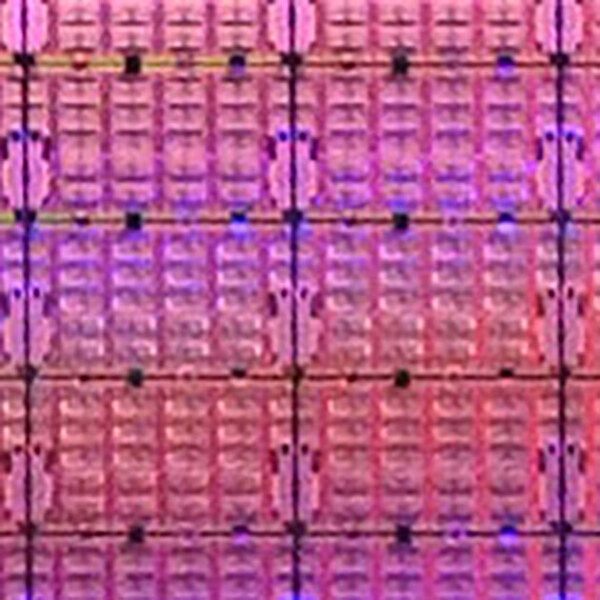

Granite Rapidsのウェハー中央部を切り抜いたのが下の画像で、縦方向に5本、横方向に6本のメッシュが通っているように見える。

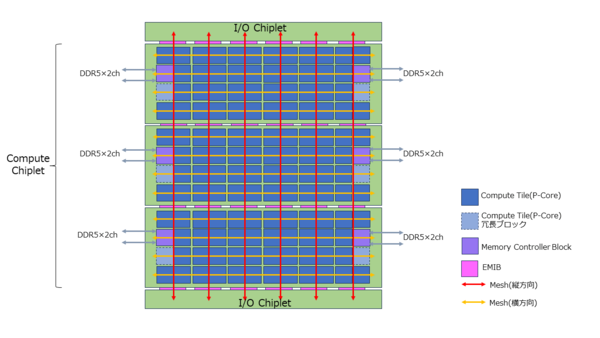

連載736回でGranite Rapidsの内部構造の想像図を掲載したが、その図は間違っていた。

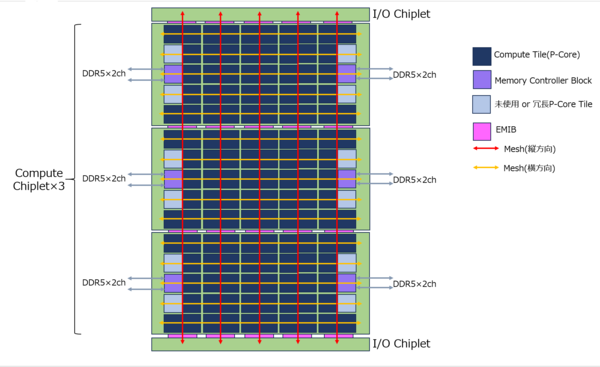

この図ではコンピュート・チップレットあたり縦方向6本、横方向5本のメッシュを想定していたが、実際の構成は下図になると想像する。

ちなみにこれは最大構成の3コンピュート・チップレットの場合で、この下に2コンピュート・チップレットで8ch DDR5の構成や、1コンピュート・チップレットで同じく8ch DDR5(これのみチップレット構成そのものが異なる)が用意されると思われる。

余談だが、そのGranite RapidsとSierra Forest、それとSierra Forestの後継となるClearwater Forestの3つの製品に関しては、正式に新しいBirch Stream Platformを使うことが明確にされた。

Sapphire Rapidsの提供が遅れたことで、Eagle Stream Platformは1年かそこらしか使われないのは少し可哀想である。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ