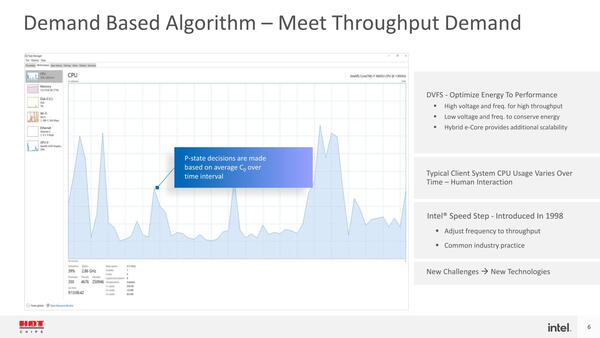

従来の省電力アルゴリズムはP-stateでの動作状況で判断

そもそも従来の省電力アルゴリズムは、DVFS(Dynamic Voltage and Frequency Scaling)に基づいて、動作周波数に応じて電圧を変化させることで最適な消費電力に抑えるのが骨子であり、その際に動作周波数を上げる/下げるの判断基準になるのが、P-stateでの動作状況、という話であった。

動作周波数を上げる/下げるの判断基準。実はこのスライドは当初は公開されていたのだが、講演時間の関係で省いたのか、最終版ではなくなっていたりする。といってもなにか妙なことが書いてあるわけでなく、一度は正式に公開されていたもので、説明にも便利なのでそのまま掲載する

要するに1998年のSpeed Stepがその大元であり、実装がより巧みになったなどの改良はあるものの、基本的にはCPUの負荷率に応じ、負荷が高まったら動作周波数を引き上げ(これに伴い電圧を上昇)、負荷が減ったら動作周波数を引き下げる(この際には電圧を下げる)仕組みである。

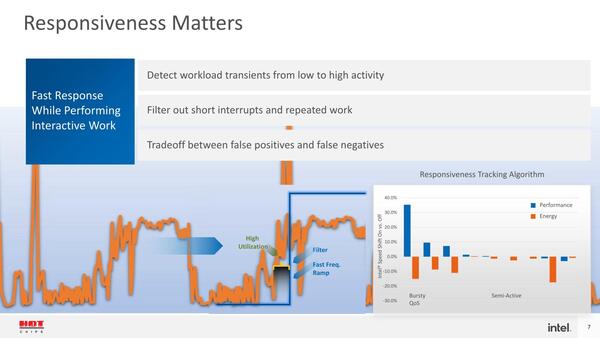

理屈は簡単だが、この仕組みの欠点は「負荷が上がってから動作周波数(と電圧)が上がるまでの間にタイムラグがある」点だ。

つまり、あるコアが最初は待機状態であるが、急に負荷が上がるとまず稼働率が100%になる。ただこの時点では、「待機状態の低い動作周波数では100%負荷になるけど、動作周波数が上がるとそれほどの負荷ではない」のか「最高動作周波数でも100%負荷になる」のかの判断は付かない。あと、割り込み処理のように一時的に負荷が高いがすぐ終わる可能性もある。

したがって、通常負荷が100%になってもわずかな時間はそのまま維持して負荷状況の変動を見る。この間も100%に張り付きっぱなしであれば、これは本当に負荷が高くなったと見なして動作周波数と電圧を引き上げるわけだ。

余談ながら、上の画像ではいきなり動作周波数が引き上げられているが、実際はもう少しステージがある。というのは動作周波数の方はベースクロックに対する倍率を変化させるだけなので、上げるのはそう難しくない。

実際にはいきなり動作周波数が大きく変わると、回路の誤動作が起きる場合があるので段階的に上げるのだが、それでもそれぞれの段階に要する時間はそれほど長くない。

しかし、電圧の方は外部のVRMを操作する関係で、急に0.6Vから1Vまで引き上げるわけにはいかない。

少し古い情報だが、インテルのVRM 11.1の仕様書によれば、電圧の変動は2.5マイクロ秒ごとに12.5mV刻みとされており、0.1V変化させるのには20マイクロ秒ほどを要する(最新のVRMはもう少し高速だと思うが)。

この数字のままでは0.6Vから1Vに引き上げるのには80マイクロ秒ほど必要で、これはGHzオーダーで動作するCPUにはかなりの長期間になる。要するに、電圧を上げ始めた頃には負荷が軽くなり始めている可能性もあるわけだ。

Meteor Lakeでは動作周波数や電圧変更をAIが判断する

では先行して少しでも負荷が上がったら、動作周波数や電圧をすぐに引き上げるか? というと、今度は無駄に動作周波数と電圧が上がってしまう可能性がある。早すぎると無駄が多く、遅すぎると性能の足かせになるわけだ。

これは逆に動作周波数や電圧を落とす方も同じだ。少しでも負荷が下がったら落とすか、負荷が下がって一定時間たったら落とすかは、性能と消費電力の両方に影響を与える。

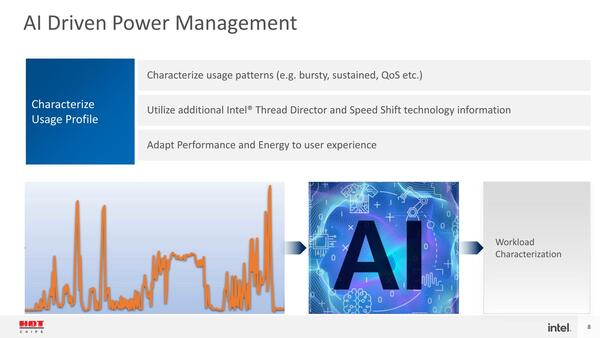

結果、どの程度のタイミングで動作周波数や電圧を変化させるかは、性能と消費電力のトレードオフの関係にある。この判断にAIを使うようにしたのが、今回の発表の骨子である。

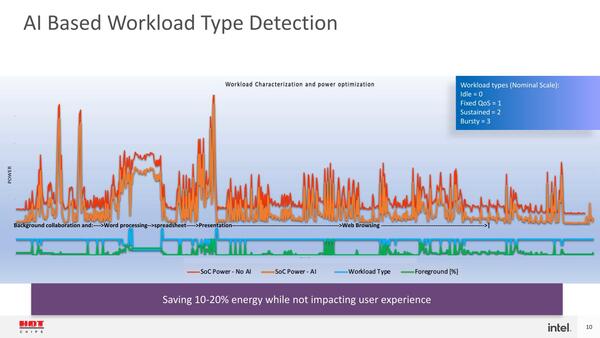

具体的には、ワークロードタイプ、つまりどんなタイプの処理をしているのかを、Idle/Fixed QoS/Sustained/Burstyに分類し(この分類にAIを利用しているものと思われる)、それぞれのタイプに応じて動作周波数の変更や電圧制御をすることで、性能を犠牲にせずに消費電力を10~20%下げられたとしている。

Idleは無負荷状態、Sustainedは長時間のワークロードが発生している(例えばExcelで巨大なワークシートの再計算をしているなど)、Burstyは割り込み処理など、Fixed QoSはおそらくだがOSのサービスなど「一定時間内に一定の処理量を必要とする」ものと思われる。

ちなみにこのグラフはThread Directorが絡まない、つまりE-Coreのみ(かP-Coreのみか)での話であり、実際にはP-CoreとE-Coreのどちらを使うかというThread Directorへの指示も実際には絡んでくるものと思われるのだが、そのあたりの詳細は今回は未公開だった。いずれMeteor Lakeが正式発表された後あたりには詳細が公開されるかもしれない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 - この連載の一覧へ