3次キャッシュを削減してコアの密度を上げた

Bergamo

EPYC 9004シリーズの発表会では一切言及されなかったのだが、事前説明会の折に「GenoaとBergamoの相違点はここだけ」として示されたのが下の画像だ。

そもそもBergamoはより高密度なサーバー向けであり、プラットフォームは既存のGenoaと共通で、コア数が最大128になる、というのが事前に説明された情報のすべてであるわけで、それもあって筆者は連載643回ではArmのbig.LITTLEに似た効果を、ただしより少ない労力で実装する形になると予測。物理設計時のライブラリーを変更するかもしれないと判断したわけだが、もう少し簡単に3次キャッシュを削減する形でコアの密度を上げる形にしたようだ。

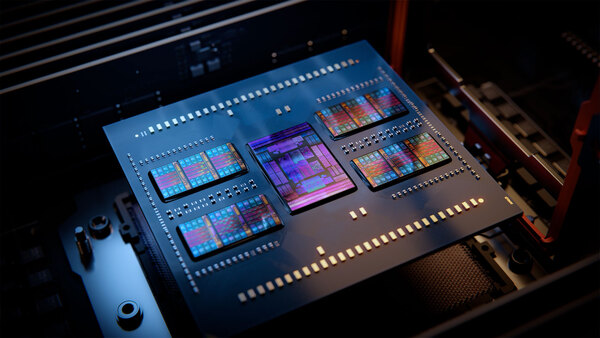

実際、これでかなり高密度化ができる。下の画像は今回発表されたEPYC 9004のパッケージ写真だ。

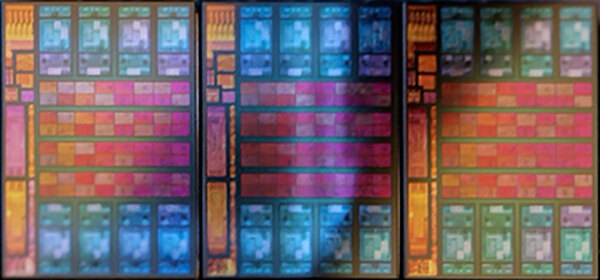

ここから3つのCCDを抜き出したのが下の画像である。このCCD1つあたりの3次キャッシュが占める面積は35%ほど。CPUコアよりはやや小さい程度であるが、インフィニティ・ファブリックのI/Fがある分これ以下にはできない感じだ。

さて、ここで仮に3次キャッシュのサイズを半分にすると、ダイサイズはZen 4の82.4%ほど、1MBまで減らすと73.7%ほどまでダイサイズが減る計算になる。試しに3次キャッシュを1MB/コアまで減らし、その代わり2 CCXを1つのダイに収めた場合のシミュレーション画像が下の画像だ。

インフィニティ・ファブリックのPHYのサイズは減らせないし、仮に2CCXになるとすると2つのCCXで1つのインフィニティ・ファブリックのI/Fを共用する部分で追加の回路が入る、と判断してこんな感じになった

ダイサイズは34.9%ほど増える計算になるが、これが8ダイでも12ダイのEPYC 9654よりは小さい(Zen 4の10.8ダイ相当になる)。パッケージの再設計は免れないが、Genoaと同じサイズにできるだろう。実のところ、なぜ2つのCCXを1つのダイに入れる案を出したかと言えば、理由は2つある。

まず、IODは最大12個のCCDを接続できる。ということは、128コアのBergamoでIODを再利用したければ、CCDあたり13個という変な数になってしまう。むしろ16コアのCCDを8つ接続する方が考えやすい。Bergamo用のIODを別に用意する案もあるだろうが、検証の手間が大幅に増えることを考えるとあまり賢明な案ではない。またCCXそのものを16コアに拡張するのは、AMDの設計のポリシーから外れる。

次に、Radeon RX 7000シリーズのところでも出た話だが、PHYのサイズは減らない。インフィニティ・ファブリックのPHYはCPUコア+3次キャッシュ32MBの高さにちょうど合う感じであり、仮に3次キャッシュを4MB(1MB/コア)まで減らしてもPHYの高さは減らないので、無駄なダイエリアができてしまうことになる。であれば、3次キャッシュ4MBのCCXを2つ縦に並べた方が効率が良いことになる。

もちろんこれは筆者の推定で、この通りになる保証はまったくない(そしてご存じの通り筆者の推定はけっこう間違う)わけではあるが、激しくは外していないと思う。

おそらくBergamoは動作周波数も2GHzかその程度に抑えられるだろう。この程度まで抑えられれば、3次キャッシュの少なさもメモリー帯域の高さでカバーできる。

コアあたりの性能は当然落ちるが、そもそもBergamoはクラウドなどに向けた高密度サーバー向けだから、個々のコアの性能そのものはそこまで重要ではない。そしてAMDの利用するTSMCのN5プロセスは、2GHz付近での性能/消費電力比は非常に良い。重要なのは性能/消費電力比であることを考えると、Bergamoは結構良いバランスの製品に仕上がる可能性が高い。

最初のところで書いた型番は、例えばBergamoがEPYC 7004やEPYC 6004などになる可能性がある。おそらく現行の9はGenoa(とこの後出てくるGenoa-X)のみで、Bergamoは別の番号になるだろう。そのあたりまで含めて今回7から9に上げた、というふうに筆者は考えている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 - この連載の一覧へ