2015年にBostanをサンプル出荷

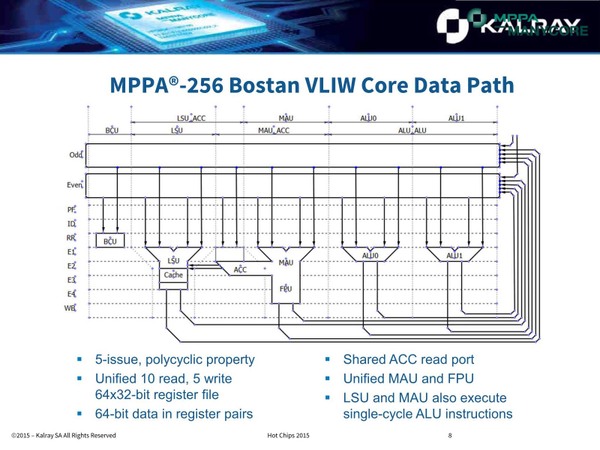

Bostanコアの詳細が下の画像だ。ALU×2、MAU(MAC Unit)×1、LSU(Load Store Unit)×1、コプロセッサーの5命令の同時実行が可能な構成で、パイプラインは最大7ステージである。分岐は3サイクル程度で処理できる。

Bostanの場合、データパスは原則32bitで、64bitデータは32bitレジスター×2をペアにして格納する形になっている。ALUは当然整数演算なので、浮動小数点演算はMAUを使って処理する格好だ。このALUが一番パイプラインが長く、実行に4サイクルかかっている。とはいえスループットそのものは1なので、けっこうな処理速度ということになる。

図がわかり難いのだが、例えばMAUの場合Odd BankとEven Bankからそれぞれ3本づつのパスが伸びている。Y=AXB+Cを計算する際に必要となるA・B・CがこのEven/Odd Bankから供給されるわけで、つまり1つのMAUでは同時に2つのMAC演算が可能になる仕組みだ。これはALUも同じで、要するに1サイクルあたり4つの32bit演算(あるいは2つの64bit演算)が可能である

結果として、600MHz駆動のコアであればMAC演算を1サイクルあたり2つということで2.4GFlopsという計算になる。ちなみにBostanではコプロセッサー命令は暗号化/復号化やCRCなどの命令に割り当てられている。

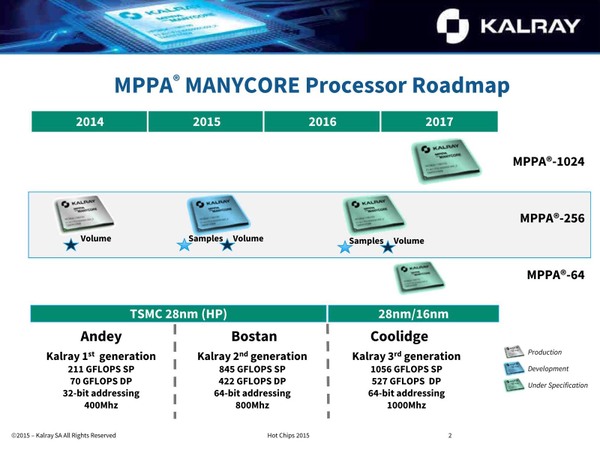

さて、KalrayではこのBostanを2014年にテープアウト、2015年にサンプル出荷を開始している。製造はTSMCの28nm HPで、600MHz動作で634GFlopsを25Wで実現する。ちなみに256コアだと634GFlopsではなく614GFlopsになるはずなので、634GFlopsというのは計算用ではなくマネジメント用の16コアのうち半分の8コアも計算にまわした264コア構成での数字のようだ。

1Wあたりの処理能力は25.36GFlopsになり、これは例えばインテルのXeon Phi(2147GFlops/300Wで7.16GFlops/W)やNVIDIAのTegra 4(75GFlops/8Wで9.38GFlops/W)などと比べてもおそろしく性能消費電力比が高い数字となっている。

実はこのBostanに先立ち、2013年にテープアウト、2014年に量産を開始したAndeyという第1世代のMPPAチップがあった。

こちらは32bitアドレスだし、コアの数は同じながら1サイクルあたりの処理性能はBostanの半分程度だったようだ。BostanはこのAndeyをベースに規模を倍増させ、動作周波数を引き上げたモデルということになる。これに続き、第3世代のCoolidgeの設計に入っている、というのが2015年における状況だった。

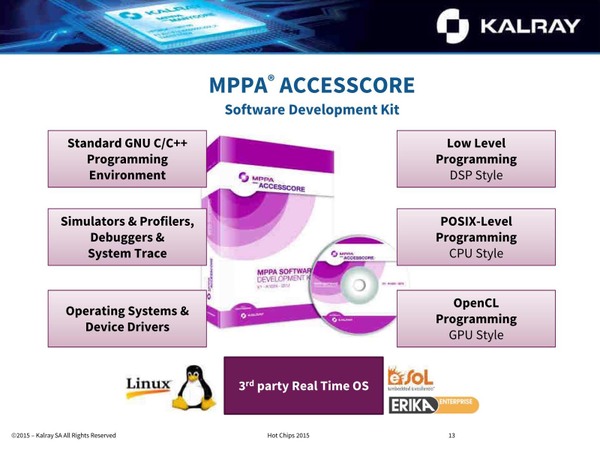

多くのサードパーティーがソフトウェアを提供

MPPAのもう1つの特徴がソフトウェアのサポートである。2015年の時点でNode OSという独自のOSとSMP Linux、サードパーティーのRTOSが提供されたほか、GNU C/C++とデバッガー/トレーサー、さらにOpenCLでのプログラミング用ライブラリーと、必要に応じてDSPスタイルのLow Level Programming Language(要するにアセンブラ+α)が提供されている。

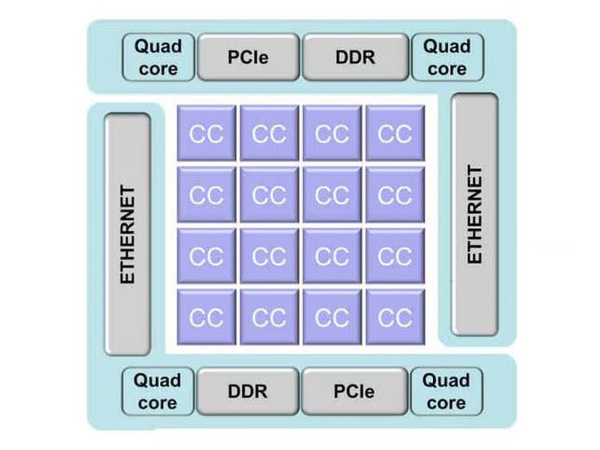

ちなみにSMP Linuxは、下の画像で言えば、全体の四隅にある“Quad core”と書かれた制御用の4コアのどれか1つで動作し、I2CやSPI、GPIO制御用のドライバーなども提供される。残りの3つのQuad coreは、メインの計算用CPUクラスターの制御に利用される格好だ。

そのメインの計算用CPUクラスター(というより各々のコア)上では独自のNode OSが動く格好だが、これはPOSIXのThreadをサポートし、GCCベースのOpenMPを利用してのコア間の同期なども取れる。なお、1コアあたり1スレッドでの動作となっている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 - この連載の一覧へ