プロトタイプでLinux動作を確認

2023年前半に量産出荷予定

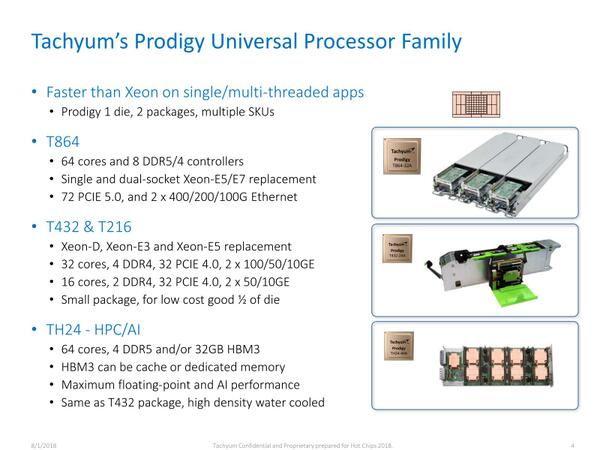

ちなみにこの2018年時点でTachyumの考えていたラインナップは下の画像の通り。ハイエンドが64コアのT864で、その下に32コアと16コアのT432およびT216がラインナップされる。それとは別に、HPC向けにT864のメモリーチャネルを半減させ、高密度化したTH24という製品も予定されていた。

さてその後はどうなったか? であるが、やはりTSMC N7でこれはいろいろ無茶があった。一応チップの製造には成功したようで、2019年にはLinuxの稼働を確認したというリリースも出ている。ただ、製品向けに改めて設計をやり直したようだ。

2021年3月にFPGAベースでのプロトタイプが稼働を開始、同年8月にはそのプロトタイプ上でのLinux動作を確認している。今年7月1日には評価用プラットフォームのプレオーダーを受け付け開始しており、今年中に評価プラットフォームの出荷、来年前半に量産出荷を開始の予定となっている。

構成も少し変化しており、CPUコアのベクトルユニットは1024bit幅に拡張、仮想化の機能も搭載された。また“Out-of-Order, 4 instructions per clock”の文字も踊っているが、これは2018年発表のものと同じで、単に最大4命令BundleのVLIWのままな気がする。

またキャッシュはL1が命令/データともに64KBに増量、DDR5-6400×8chをサポートになった(HBM3はもう構成から落ちた模様)。PCIe 5.0は最大64レーンになっている。製造プロセスはTSMCのN5に変更になり、VLIWのネイティブISA以外にx86/Arm/RISC-Vのバイナリーをエミュレーション動作できるとされている。

ラインナップは以下の表の通り。AI性能に関しても公開されたあたりが、以前と異なる点である。

| Prodigyのラインナップと性能 | ||||||

|---|---|---|---|---|---|---|

| 製品 | コア数 | メモリー | PCIe | AI性能 | HPC性能(DP) | |

| Prodigy T832 | 32 | DDR5-6400×8 | x32 | 1.5PFlops | 12TFlops | |

| Prodigy T864 | 64 | DDR5-6400×8 | x32 | 3PFlops | 23TFlops | |

| Prodigy T16128 | 128 | DDR5-7200×16 | x64 | 12PFlops | 90TFlops | |

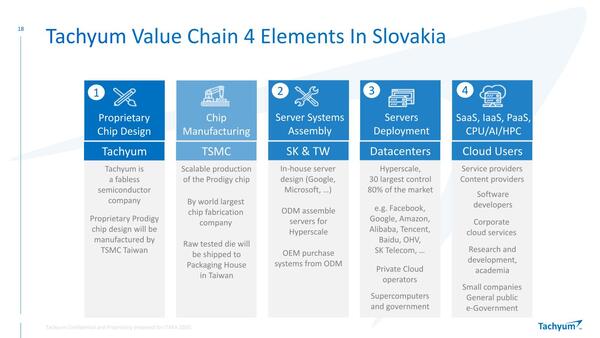

ところで冒頭、スロバキアとのつながりが強いと説明したは、2020年のITAPAにおけるTachyumの発表スライドの1枚が下の画像だ。

Tachyumはデザインセンターをスロバキアに2ヵ所(ブラチスラヴァとコシツェ)抱えており、チップ設計とアセンブリ、サーバー機器の製造、サービスの提供をスロバキアで行なっている、としている。現状ではまだチップもないため、AI性能を評価するのは時期尚早だが、ある意味(VLIWとはいえ)控えめな構成でどこまで性能を上げられるのか、というのは興味深い。来年あたりのMLPerfに数字が上がることを期待したい。

この連載の記事

-

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 - この連載の一覧へ