ロードマップでわかる!当世プロセッサー事情 第672回

Navi 3を2022年末、Instinct MI300を2023年に投入 AMD GPUロードマップ

2022年06月20日 12時00分更新

Instinct MI300を2023年に投入

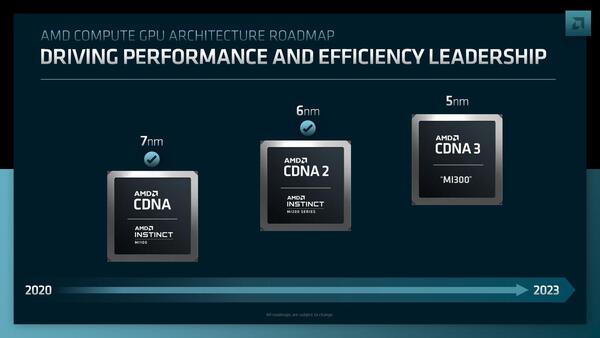

次はCDNA側だが、こちらは2023年までのロードマップとなった。

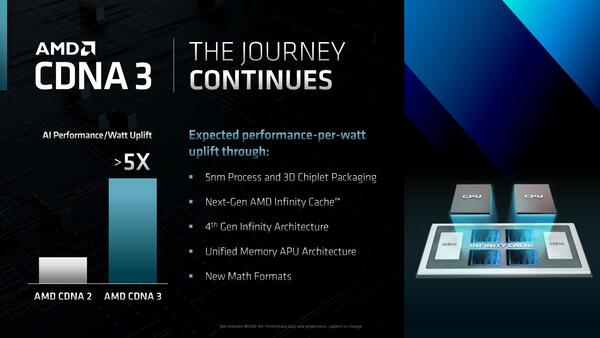

その次世代製品は2023年に投入されるInstinct MI300となるが、こちらは以下の点が挙げられている。

- 5nmプロセスを採用

- 3D Chiplet構成と明示しているあたり、3D V-Cacheの搭載は確定的

- 第4世代Infinity Architectureを採用

- 後述するUnified Memory Architectureを採用

- 新しいMath Formatをサポート

まず3D Chiplet。下の画像の右の図で見る限り、GPUダイにInfinity Cacheダイが接続する構成に見える。もともとInstinct MI200では連載635回で説明したように2次キャッシュはあったものの、Infinity Cacheのような大容量キャッシュは搭載していなかった。理由は単純で、XCUの数が多すぎてダイサイズがギリギリであり、さらに大容量キャッシュを積むゆとりがなかったからだ。

しかし、Infinity Cacheの効用はRadeon RX 6000シリーズでも明確であり、HBM(おそらくInstinct MI300ではHBM3だろう)は帯域は大きいもののレイテンシーも大きいから、この間を埋める大容量キャッシュがあれば、コアをフルに稼働できる。

もっと言えば、Frontierの高い性能/消費電力比の理由を連載670回で説明したが、もう無理に動作周波数を上げるよりも、そこそこの動作周波数に抑えて効率を上げる方がトータルでは良い結果になることが見えている。

Frontierにしても、仮にEPYCを2.2GHz、Instinct MI250Xを1.7GHz駆動にすれば、ノードあたり196TFlopsになり、ノード数そのものは8500弱まで減らせる計算になる。ノードが減ればその分通信のレイテンシーも減る……はずではあるが、9248ノードを8500ノードまで減らしても、ネットワークトポロジーそのものは変わらない(例えば3段のFat Treeが2段にできるか? と言えば無理だろう)と思われるので、レイテンシーそのものはほぼ変わらず、効率は大して変わらない。

その一方でノードあたりの消費電力は2.7KWほどになり、システムの消費電力は23MWを超えることになる。ランニングコストの大半が消費電力であることを考えれば、フル駆動という案はないだろう。

さてMI300に話を戻すと、おそらくTSMC N5はN7比でロジック密度は最大80%増しとされるが、N7→N6でロジック密度が18%増しだったことを考えると、N6→N5、つまりMI200からMI300では多くて5割増しといったところだろう。

MI200が128XCUだったから、192XCUくらいだろうか? MI200が4つのCompute Engineだったものを6つに増やすという程度だろう。ただしこれを常にフルに動かしきれるか? というと、おそらく相応のメモリーアクセス待ちが発生するから効率はそれほど高くないと考えるのが自然だ。

ところがInfinity Cacheを追加すれば、このメモリーアクセス待ちが大幅に改善されることが期待できる。するとMI300の実効性能そのものを高くとれるから、動作周波数をやや下げても問題ない、という話になる。要するに性能を下げずに消費電力を下げるための手段としてInfinity Cacheの搭載が有効なわけだ(これはRyzen 7 5800 X3Dでも同じだ)。

ところで物理的にこのGPUダイとInfinity Cacheのダイがどうとながるか? であるが、おそらくGPUダイそのものはInstinct MI100/200と同じく700mm2程度の巨大なダイサイズが今回も継承されると考えられる。

となると、Ponte VecchioのRAMBO Cacheのように、Infinity Cacheの方は複数のGPUダイにまたがる巨大なものにはならない(できない)ことになる。ステッパーの露光寸法の限界(最大でも8002mm強)に引っかかるからだ。むしろ歩留まりを高めるためには、もっと小さいサイズに分割した方が効果的である。

別にInfinity Cacheが2バンクではいけない理由もない。Infinity Cacheの方は300mm2弱で、256MB程度の容量の確保は難しくないだろう。チップ全体では512MB程度のキャッシュが使えれば、かなり性能向上(というより性能低下防止)に効果的だろうと考えられる。

新しいフォーマットは、FP8のサポートだろう。FP8は連載661回で紹介したが、NVIDIAのHopperが初採用したフォーマットである。

この連載の記事

-

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 -

第857回

PC

FinFETを超えるGAA構造の威力! Samsung推進のMBCFETが実現する高性能チップの未来 -

第856回

PC

Rubin Ultra搭載Kyber Rackが放つ100PFlops級ハイスペック性能と3600GB/s超NVLink接続の秘密を解析 - この連載の一覧へ