拡張用にTSVが埋め込まれているZen 3コア

64MBのダイは3D V-CacheにもTSVを実装して実現か?

直接Ryzen 7 5800X3Dには関係ない話であるが、その3D V-Cache周りの話が昨年のFall Linley Processor Forumで出ていたのでついでに解説しよう。フォーラムで説明したのは、そのLinley Groupの親会社であるTech Insightsである(両社の関係は連載640回の冒頭で触れている)。

Tech Insightsによれば、そもそもZen 3コアのL3 Blockには将来の拡張用にTSV(Through Silicon Via:シリコン貫通型ビア)が埋め込まれており、その本数はおよそ2万3000本だという。

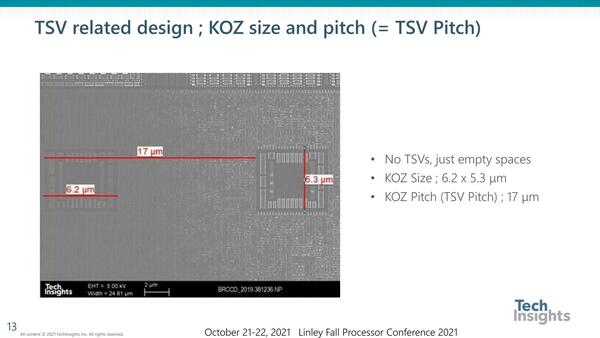

このTSVが埋め込まれている領域の中には一定間隔でKOZ(Keep Out Zone:TSVを配しない領域)が必要になる。KOZを設ける理由は、TSVを利用するとCTE(Coefficient of Thermal Expansion:熱膨張係数)にミスマッチが発生するためだ。

TSVは銅で構成されるが、これとシリコンでは熱膨張係数が異なる。したがって実際に通電するとTSV周辺に熱膨張に起因する応力が発生する。この応力を逃がすために、TSV周辺をある程度空けておく必要がある。下の画像がそのKOZのアップであり、KOZのピッチがそのままTSVのピッチとなる形だ。

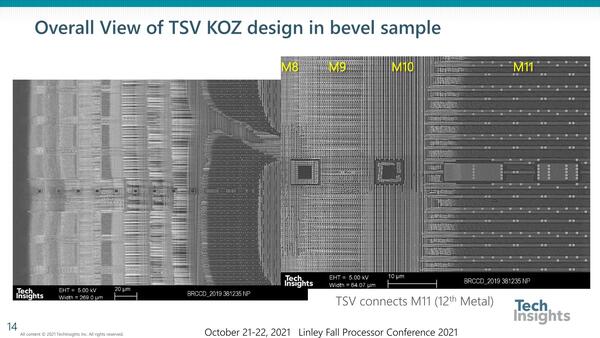

下の画像は、M2~M11の各配線層におけるTSV(&KOZ)の構造を断面図的に並べたものである。

左と右では縮尺がだいぶ違うのでわかりづらいかもしれないが、左がM2~M11までの各層を並べたもの、右がそのM8~M11までを拡大したものである。要するにM2~M11までVIA(とKOZ)の寸法は変わっておらず、一定の太さのTSVが配線層を貫通していることことになる。

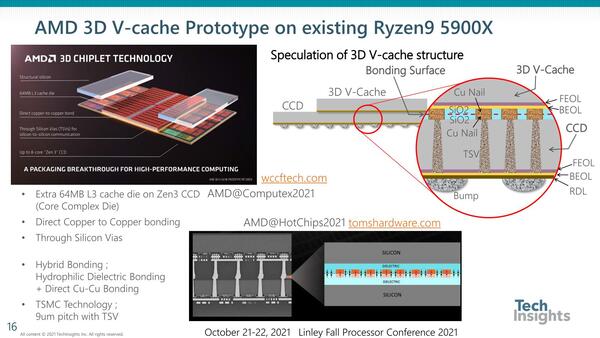

下の画像は走査電子顕微鏡を使った分解写真ではなく、想定される接続部の構造である。

FEOL(Front End Of Line)がトランジスタ層、BEOL(Back End Of Line)が配線層、RDL(Re-distribution Line)が再配線層、つまりインターポーザーやパッケージ基板となる。

CCDそのものはFlip-Chip、つまりダイを裏返した状態で実装されるのが一般的であり、TSVはBEOL(配線層)からFEOL(トランジスタ層)を突き破る形でダイの裏側に伸びた形で実装されていると見られる。

3D V-Cacheも同じくFlip-Chipの形で実装されるが、こちらはTSVを必要とせず、TSVからの信号をそのままCu Nail経由でBEOLで受け、SRAMが実装されるFEOLにつなぐ格好になっている。

この推定はリーズナブルなのだが、1つ疑問なのは3D V-Cacheの構造である。以前に連載618回で説明しており、現在もこの案を信じているのだが、実際には3D V-Cacheのダイは1枚あたり32MBであり、これを2枚重ねて64MBとしていると思われる。

上の画像はそうではなく、64MBのダイが同じサイズで実装できる、という前提に立ってのものであり、実際には3D V-Cacheの中にもTSVが実装されている可能性がある。

現時点ではどちらが正しいのかは不明である。実は2月20日から開催されるISSCC 2022のAdvanced Programの中で、AMDはこの3D V-Cacheの詳細を公開することを明らかにしているので、詳細がわかったらまたレポートしたい。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 -

第860回

PC

NVIDIAのVeraとRubinはPCIe Gen6対応、176スレッドの新アーキテクチャー搭載! 最高クラスの性能でAI開発を革新 -

第859回

デジタル

組み込み向けのAMD Ryzen AI Embedded P100シリーズはZen 5を最大6コア搭載で、最大50TOPSのNPU性能を実現 -

第858回

デジタル

CES 2026で実機を披露! AMDが発表した最先端AIラックHeliosの最新仕様を独自解説 - この連載の一覧へ