ロードマップでわかる!当世プロセッサー事情 第634回

ネットワークに特化したIPUのMount Evansでシェア拡大を狙うインテル インテル CPUロードマップ

2021年09月27日 12時00分更新

Intel Architecture DayとHotChipsでの情報アップデートの最後はIPUの話だ。そもそもIPU(Infrastructure Processing Unit)とは何? というところから始めよう。IPUそのものは今年の6月に開催されたSix Five Summitというイベントで初めて発表されたものだが、名前の通りインフラストラクチャー(つまりネットワーク周り)の処理を行なうためのプロセッサーである。

こう言ってもわかりづらいと思うのだが、実はASCII×TECHの記事にIPUの必要性が余すことなくまとめられている。この記事はマイクロソフトのAzureの内部構成を説明したものであるが、マイクロソフトは以前からAzureの足回りにまずFPGA、ついでASICを自社開発してFPGAを置き換える形で利用している。

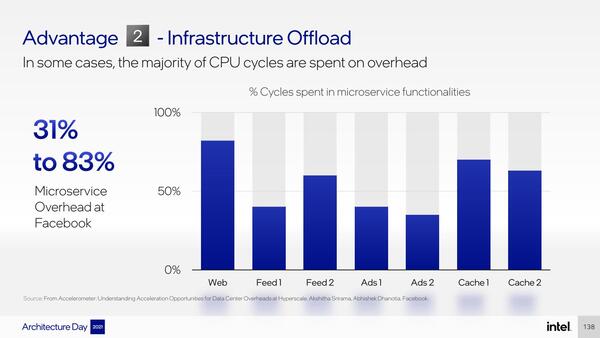

その理由は記事にもあるように「インフラ処理でCPUを使ったら負け」だからだ。ネットワーク周りの処理は、なるべくNICのそばで、しかもCPUを介さずに行なった方が効果的というわけだ。

ただ、いくら「インフラ処理でCPUを使ったら負け」と言われても、それをFPGAベースに置き換えたり、さらにそれをASICに置き換えたりできるのは、膨大な数のサーバーを運用しているうえ、FPGAやASICの開発エンジニアをかき集めることも含めて、ものすごい金額の開発費を投じられるマイクロソフトクラスの企業だから言える話で、それこそ自社でクラウドサービスを運営しているGAFA(Google/Amazon/Facebook/Apple)やBATH(Baidu/Alibaba/Tencent/Huawei)規模でないと、手が出せない。

こうした企業の場合、データセンターの運営費(≒電気代+空調費)をどうやって下げるかが最大の関心事であり、インフラ処理をFPGAやASICで置き換えることで電気代が下げられれば、そう長い期間をかけずに開発費などが回収できてしまう。しかし、これは普通の企業には到底真似できない芸当である。

そこで、ネットワーク処理に特化したプロセッサーを開発し、これにインフラ処理を行なわせることで、ASICには負けるにしてもFPGAと同程度の効率を実現させようというのがIPUの狙いである。

もちろんFPGAでも良い(後述するがIPUの第1世代はFPGAベースである)のだが、これだと扱えるエンジニアが限られてしまう。ウェブサービスのエンジニアレベルとまでは言わないものの、普通にCPU向けのコードを書けて、必要ならアセンブラリストを眺められる、つまりインフラエンジニアやデバイスドライバーなどを扱えるエンジニアなら利用できる程度にするためには、汎用プロセッサー+アクセラレーターの体裁をとることが望ましい。

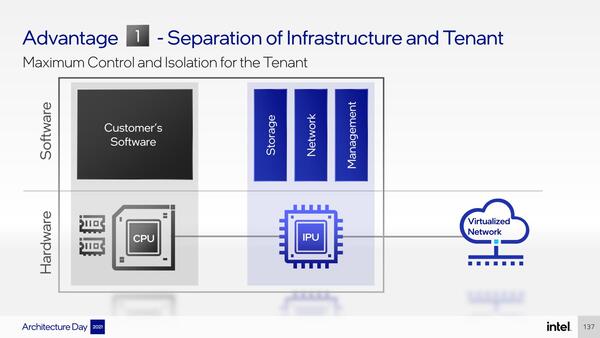

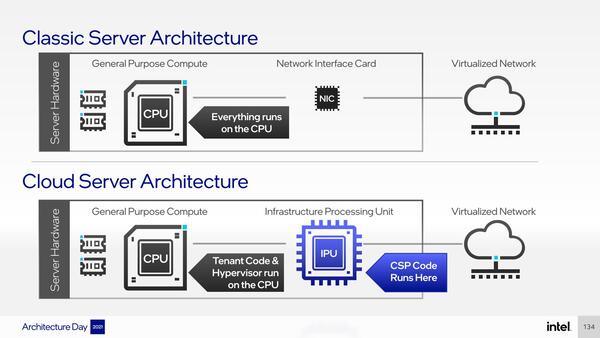

このあたりの関係をまとめたのが下の画像である。要するにインフラ回りの処理(主にネットワーク系)は、CPUまで持ち上げる手前でIPUで処理してしまえ、ということだ。

IPUを置くメリット。CSPはCloud Solution Providerの略で、クラウドサービスで必要とされる処理はIPUで行ない、CPUは実際に(クラウドの顧客が)動かしたいコードに専念させる仕組みだ

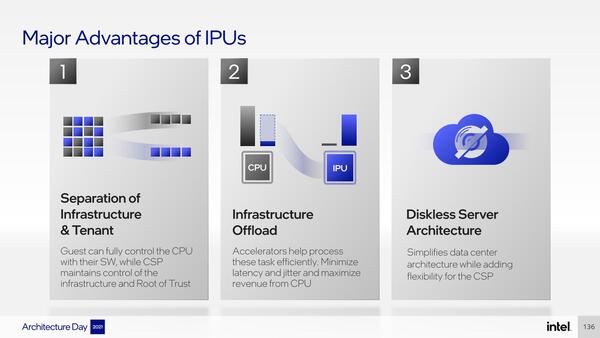

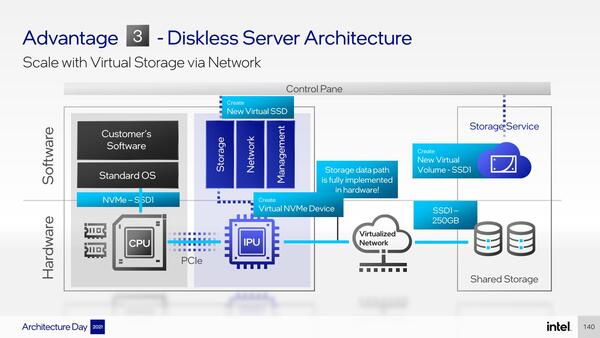

IPUのメリットはいくつかある。下の画像はこれをまとめたものだ。

・CSPをユーザーが使うCPUと物理的に分離することで、管理しやすくできるし、セキュリティー面でも強化できる。

・CPUの能力をユーザーに100%割り振れる=ユーザーからそれだけ収入を得やすくなる。

・ストレージ管理処理をIPU側に任せることで、ローカルストレージとネットワークストレージを(CPUから見ると)同じように扱えるようになる。これにより、ローカルストレージを置く必要がなくなる。

・CSPをユーザーが使うCPUと物理的に分離することで、管理しやすくできるし、セキュリティー面でも強化できる。

これはクラウド事業者向けのメリットではあるが、自社サーバーであってもプロセッサーを効率的に使えるほか、ネットワーク関連処理をより高速化できるというメリットもあるので、IPUが実装されることは悪い話ではない。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ