AMDは3月15日に第3世代EPYCを、3月16日にRyzen Pro 5000 Mobileをそれぞれ発表、そして3月26日にはThreadripper Proを発売した。この3つについてそれぞれ簡単に説明しておきたい。

より少ないDIMMでフルに性能が出せる

第3世代EPYC

まず最初はMilanというコード名で知られる、第3世代EPYCである。こちらはローレンス・バークレー国立研究所内のNERSC(National Energy Research Scientific Computing Center)に2020年末までにインストールされるPerlmutterが最初の大規模システムとなるというのは連載510回ですでに説明した通り。

実際のタイムラインを確認すると、2020年の11月から納入がスタートしており、2021年3月までにハードウェアの納入が完了。2021年第2四半期にNERSC側の環境設定などを含むシステム構築が始まる格好になっており、やや遅れてはいるが、1四半期程度のずれであれば許容範囲であろう。

連載597回で説明した「すでに一部の顧客には出荷開始されている」というのは、このNERSC向けのPerlmutterと思われる(これだけではなく、ほかにもありそうであるが)。

その第3世代EPYC、基本的にはZen 3コアのCompute Die×8+I/O Dieの構成であり、既存の第2世代EPYCとDrop-in Compatible(つまりBIOSの入れ替えだけすればそのまま装着可能)となっている。加えて、セキュリティー機能の拡充や4/6chメモリーのサポートも新たに追加されている。

この結果、I/O Dieに関しても基本的には同じだが、セキュリティーやメモリーコンローラーに変更が加えられたそうで、第2世代EPYCとは異なるものになっているそうだ(大変更というほどではないようだが)

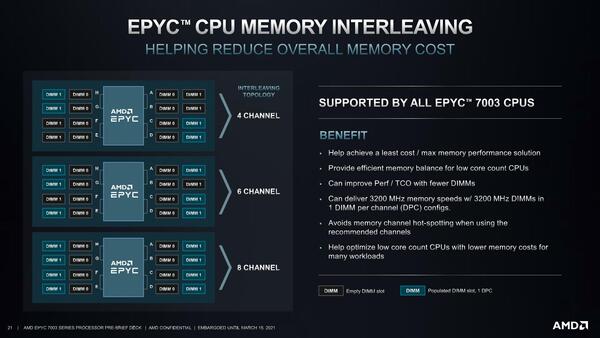

性能面の話は後でするとして、まずはメモリー周りについて。第2世代EPYCでは、メモリーインターリーブが動くのは、8本のメモリーチャンネルすべてにDIMMが装着されている場合で、なので性能を出そうとするとDIMMが8枚の計16枚の構成が必須になっていた。

ただ実際にはそこまでのDIMMを差さずに運用したいというニーズが寄せられたようで、それもあって4/6チャンネルでのメモリーインターリーブもサポートすることで、より少ないDIMMであってもフルに性能が出せるように配慮されたとのことだった。ちなみにメモリー容量そのものは、最大256GB DIMMを使った場合に4TBとなっており、これは以前と変わらない。

またPCI Expressに関して言えば、コヒーレント・インターコネクトに変更があるとされる。そもそも2 Socket構成の場合、PCI Expressレーンを利用してインフィニティー・ファブリックを通す構造になっているが、このケースでは信号速度が18GT/秒に引き上げられる模様だ。

もっとも違いはこの程度。改良が加えられたのは性能とセキュリティー周りであるが、性能は後述するとしてセキュリティー周りについて。

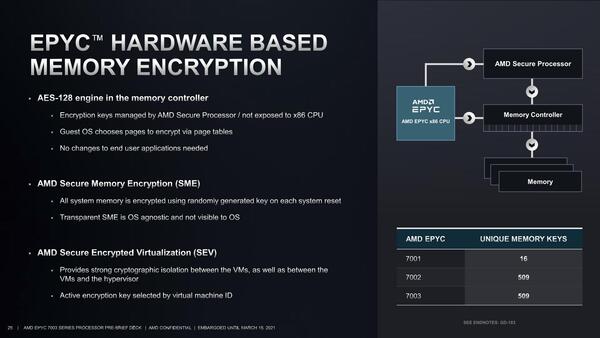

下の画像がセキュリティー関連の機能一覧である。これらはコンシューマー向けのZen 3では無効化されているが、EPYCや後述のRyzen Pro 5000 Mobileでは有効化されている。

この中でCET Shadow Stackは、今年1月のCESでIntel vProがAMDのRyzen Pro(Gen 2)よりも優れている点として示したことだが、Zen 3コアにはこれへの対抗策が実装されており、その意味ではインテルのアドバンテージは早くもなくなったということでもある。

CESにおけるビデオより。これは新しいvProに搭載されたCET(Control-Flow Enforcement Technology)を利用しての効果。ROP(Return Oriented Programming)という、プログラム内のジャンプの飛び先を書き換えることで不正なプログラムを実行するという技法に対する防御システムである

ちなみにすでに知られているさまざまな脆弱性に関してはZen 2世代から対応済であり、またメモリー内のデータの暗号化に関しては第2世代と同様の仕様になっている。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第875回

PC

1000A超のAIプロセッサーをどう動かすか? Googleが実践する垂直給電(VPD)の最前線 -

第874回

PC

AIの未来は「電力」で決まる? 巨大GPUを支える裏面給電とパッケージ革命 -

第873回

PC

「銅配線はまだ重要か? 答えはYesだ」 NVIDIA CEOジェンスンが語った2028年ロードマップとNVLink 8の衝撃 -

第872回

PC

NVIDIAのRubin UltraとKyber Rackの深層 プロトタイプから露見した設計刷新とNVLinkの物理的限界 -

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 - この連載の一覧へ