ロードマップでわかる!当世プロセッサー事情 第584回

性能/消費電力比がCore i9の2.8倍というRyzen 5000シリーズの詳細 AMD CPUロードマップ

2020年10月12日 12時00分更新

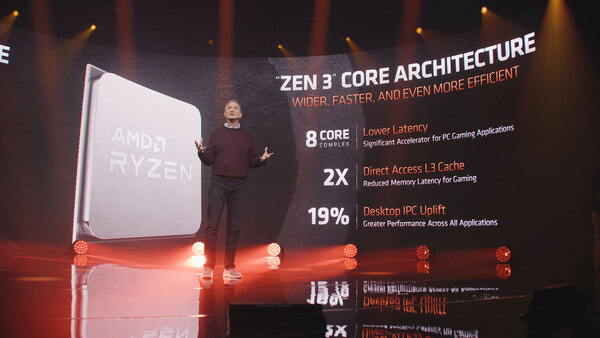

Zero Bubbleで分岐予測精度を向上

Branch Predictorには新たにZero Bubble Branch Predictionを採用したとする。実はAMDは2013年に“Bandwidth increase in branch prediction unit and level 1 instruction cache”という特許を取得している。

この特許では分岐予測の処理の中で“One Bubble”(No-Operationな1命令)を追加することで、BP(Branch Prediction)とHP(Hash Prediction)の両方をうまく動かせ、結果として分岐予測精度が上がるというものである。

察するに今回のZero Bubbleは、このBubbleを0、つまりNo-Operationな命令を追加せずに、例えばTagのような形でBubbleがいることを示す形で効率化を図った、というあたりに読めなくもない。

ただ実は“Zero Bubble”に関してはSamsungが“High performance zero bubble conditional branch prediction using micro branch target buffer”という特許をすでに取得済であり、これとの関係が気になるところである。

このあたりは、もう少し深い話をAMDが説明してくれるまで筆者としてもお手上げである。ただ結果として冒頭の画像のように、これでIPCが1~2%程度は改善しているようなのでバカにはできない。

Load/Storeユニットの帯域を倍増

Load/Storeに関しては、例えばAGUもひょっとすると4つになっている可能性を否定できないが、それよりもLSU(Load/Store Unit)の帯域を倍にする方が効果的だろう。実際、FPUを強化するというからには、1サイクルあたりで処理できるデータ量が増えることになる。

Zen 2のLSU周りは連載516回で示した通り、読み込み64Bytes/サイクルと書き込み32Bytes/サイクルを同時に行なえる構成になっているが、これを倍増しているのではないかと考えている。

ちなみにこのZen 3の世代ではまだAVX512をサポートするという話はない(Zen 4世代というのがもっぱらの噂である)が、FPUを増やすことでAVX256命令の処理能力を倍にするなら、LSUも相応に強化する必要がある。そしてこれはALUの処理性能向上にもつながることになる。

キャッシュのプリフェッチについては、正直よくわからない。あるいは3次キャッシュの容量が実質倍になったことに向けて、アルゴリズムや実装を強化したのかもしれない。

さて、ここまでコアの内部を強化すると、当然コアのエリアサイズが増える。それにもかかわらず、ダイサイズがほぼ変わらないように見える。

後述するように3次キャッシュのトータルサイズは変わらない。ここで効いてくるのが、冒頭で書いた「N7→N7+ではトランジスタ密度が1.2倍になる」という話である。今回、プロセスの変更で増えたトランジスタは、すべてコアの改良につぎ込んだのではないかと思う。

おそくCCDダイの原価そのものはほとんど変わらないであろう。なぜなら、ArF→EUVでマスクコストは減るが、EUVを利用することによるコストアップで相殺されるからだ。このあたりの話は連載581回で説明している。それでもIPCの向上につながるのなら、これは大きなメリットであろう。

ついに8コアになったCCXと

容量が2倍になった3次キャッシュ

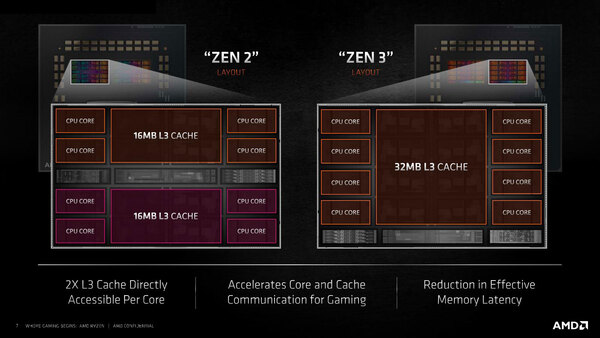

次にCCX(Core Complex)周りについて。Zen 3世代では、ついにCCXが8コアに変更になった。連載496回で筆者がZen 2の推定される構造の1つとして紹介した構成がやっと実現した形だ。

下の画像が内部構造であるが、やっとすっきりした形だ。

実際Zen 2までは、2つのCCXの間の通信は、一度CIoD(I/O Die)経由で行なうことになっており、32MBの3次キャッシュと言いつつも、実質的な3次キャッシュの容量は16MBに限られていた。

ところがZen 3ではこれが32MBになり、またコア間の通信も同一CCX内になるので、ずっと高速化(低レイテンシー化)された。もちろんこれはCCD(Core Complex Die)が1つの場合の話で、2つ以上では引き続きCIoD経由での通信になるので、その場合のレイテンシーは大きくなる。

ちなみにそのCIoDの話であるが、Ryzen 5000シリーズに採用されるCIoDは、Ryzen 3000シリーズのものと完全に同一である。Zen 3の世代で、AMDの開発チームはCCDの改良に全力を注いでおり、CIoDに関してはそのままとされた形だ。

もっともCIoDに手を入れる必要があるか? といえば、実はあまりない。メモリーに関してはDDR4-3200まで定格でサポートし、オーバークロック動作でもDDR4-4200+は比較的容易などと以前説明があったほどなので、改良の余地は少ない。

PCI ExpressもすでにGen 4に対応しており、まだGen 5は対応製品も存在しないので、やはりやるべきことはあまりない。

これがZen 4の世代になると、DDR5メモリーとPCI Express Gen5の対応が必要になり、マザーボードも当然変更になる(DIMMのスロットそのものが変更になる)から、当然CIoDも作り直しになる。であれば、Zen 3の世代は特にCIoDをいじらずに先送りにしよう、という発想は理に適っている。

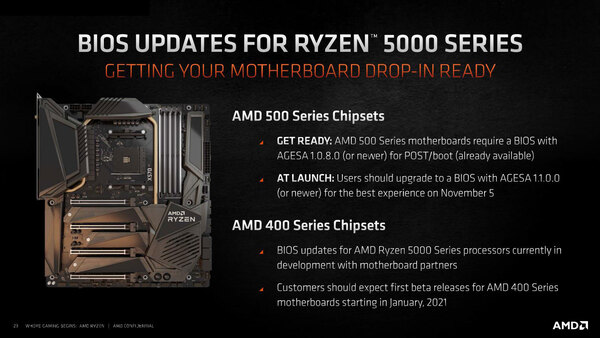

それもあってか、今回チップセットに関しては特に言及がなかった。今のところAMD 600シリーズチップセットに関しては発表がない。世代的に言えばUSB 4.0をサポートしたAMD 600シリーズが投入されても不思議ではないのだが、これは後送りになるようだ。

したがって当面はAMD 500シリーズと、AMD 400シリーズが対応するチップセットということになる。ただし発売時にサポートされるのはAMD 500シリーズのみで、AMD 400シリーズのサポートは2021年1月を予定しているという話であった。

本記事はアフィリエイトプログラムによる収益を得ている場合があります

この連載の記事

-

第871回

PC

GTC 2026激震! 突如現れたGroq 3と消えたRubin CPX。NVIDIAの推論戦略を激変させたTSMCの逼迫とメモリー高騰 -

第870回

PC

スマホCPUの王者が挑む「脱・裏方」宣言。Arm初の自社販売チップAGI CPUは世界をどう変えるか? -

第869回

PC

半導体プロセスの新たな覇権! インテルのDNNプロセッサーはAMDやMetaを凌駕する配線密度と演算密度 -

第868回

PC

物理IPには真似できない4%の差はどこから生まれるか? RTL実装が解き放つDimensity 9500の真価 -

第867回

PC

計算が速いだけじゃない! 自分で電圧を操って実力を出し切る賢すぎるAIチップ「Spyre」がAI処理を25%も速くする -

第866回

PC

NVIDIAを射程に捉えた韓国の雄rebellionsの怪物AIチップ「REBEL-Quad」 -

第865回

PC

1400WのモンスターGPU「Instinct MI350」の正体、AMDが選んだ効率を捨ててでも1.9倍の性能向上を獲る戦略 -

第864回

PC

なぜAMDはチップレットで勝利したのか? 2万ドルのウェハーから逆算する経済的合理性 -

第863回

PC

銅配線はなぜ限界なのか? ルテニウムへの移行で変わる半導体製造の常識と課題 -

第862回

PC

「ビル100階建て相当」の超難工事! DRAM微細化が限界を超え前人未到の垂直化へ突入 -

第861回

PC

INT4量子化+高度な電圧管理で消費電力60%削減かつ90%性能アップ! Snapdragon X2 Eliteの最先端技術を解説 - この連載の一覧へ